# TMS320VC547x CPU and Peripherals Reference Guide

Literature Number: SPRU038 December 2001

#### IMPORTANT NOTICE

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, license, warranty or endorsement thereof.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices. Representation or reproduction of this information with alteration voids all warranties provided for an associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Resale of TI's products or services with <u>statements different from or beyond the parameters</u> stated by TI for that products or service voids all express and any implied warranties for the associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Also see: <u>Standard Terms and Conditions of Sale for Semiconductor Products.</u> www.ti.com/sc/docs/stdterms.htm

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

### **Preface**

### **Read This First**

#### About This Manual

This user's guide serves as a reference for the Texas Instruments TMS320VC547x low-power, enhanced-architecture, dual-core digital signal processor (DSP), and is intended to assist hardware and software engineers in developing applications using this device. It describes both cores—the TMS320C54x<sup>™</sup> DSP CPU and the ARM7TDMI<sup>™</sup> microcontroller unit (MCU) —and their peripherals, together with the memory and peripheral interface associated with each core.

Throughout this book, the TMS320VC547x dual-core device is referred to as the VC547x. Where the ARM7TDMI MCU core is referred to separately, the alphanumeric designation is shortened to ARM™. Information about the two processor cores in relevant chapters is provided separately, rather than combining similar features where applicable.

#### **Notational Conventions**

This book uses the following conventions.

- ☐ Instruction Sets

- The TMS320VC547x DSP CPU can use either of two forms of the instruction set: a mnemonic form or an algebraic form. This book uses the mnemonic form of the instruction set. For information about the mnemonic form of the instruction set, see TMS320C54x DSP Reference Set, Volume 2: Mnemonic Instruction Set. For information about the algebraic form of the instruction set, see TMS320C54x DSP Reference Set, Volume 3: Algebraic Instruction Set. These references are both listed in the section titled Related Documentation From Texas Instruments.

- The TMS320VC547x MCU CPU uses its own instruction set. For information about the MCU's instruction set, see TMS470R1x User's Guide, also shown in Related Documentation From Texas Instruments.

- Program listings and program examples are shown in a special typeface.

Here is a segment of a program listing:

```

STL A,*AR1+ ;Int_RAM(I)=0

RSBX INTM ;Globally enable interrupts

B MAIN_PG ;Return to foreground program

```

Square brackets, [ and ], identify an optional parameter. If you use an optional parameter, specify the information within the brackets; do not type the brackets themselves.

#### Related Documentation From Texas Instruments

The following books provide related documentation for the TMS320VC547x. To obtain a copy of any of these TI documents, call the Texas Instruments Literature Response Center at (800) 477-8924. When ordering, please identify the book by its title and literature number. Many of these documents are located on the Internet at http://www.ti.com.

- TMS320C54x DSP Reference Set, Volume 2: Mnemonic Instruction Set (literature number SPRU172) describes the TMS320C54x digital signal processor mnemonic instructions individually. Also includes a summary of instruction set classes and cycles.

- TMS320C54x DSP Reference Set, Volume 3: Algebraic Instruction Set (literature number SPRU179) describes the TMS320C54x digital signal processor algebraic instructions individually. Also includes a summary of instruction set classes and cycles.

- TMS470R1x User's Guide (literature number SPNU134) describes the TMS470R1x RISC microcontroller, its architecture (including registers), the ICEBreaker™ module, interfaces (memory, coprocessor, and debugger), 16-bit and 32-bit instruction sets, and electrical specifications.

- TMS320C54x DSKplus User's Guide (literature number SPRU191) describes the TMS320C54x digital signal processor starter kit (DSK), which allows you to execute custom C54x™ code in real time and debug it line by line. Covered are installation procedures, a description of the debugger and the assembler, customized applications, and initialization routines.

- TMS320C54x Assembly Language Tools User's Guide (literature number SPRU102) describes the assembly language tools (assembler, linker, and other tools used to develop assembly language code), assembler directives, macros, common object file format, and symbolic debugging directives for the C54x generation of devices.

- TMS320C54x C Source Debugger User's Guide (literature number SPRU099) tells you how to invoke the C54x emulator, evaluation module, and simulator versions of the C source debugger interface. This book discusses various aspects of the debugger interface, including window management, command entry, code execution, data management, and breakpoints. It also includes a tutorial that introduces basic debugger functionality.

- TMS320C54x Code Generation Tools Getting Started Guide (literature number SPRU147) describes how to install the TMS320C54x assembly language tools and the C compiler for the C54x devices. The installation for MS-DOS™, OS/2™, SunOS™, Solaris™, and HP-UX™ 9.0x systems is covered.

- **TMS320C54x Evaluation Module Technical Reference** (literature number SPRU135) describes the C54x evaluation module, its features, design details and external interfaces.

- TMS320C54x Optimizing C/C++ Compiler User's Guide (literature number SPRU103) describes the C54x C compiler. This C compiler accepts ANSI standard C source code and produces TMS320™ assembly language source code for the C54x generation of devices.

- **TMS320C54x Simulator Getting Started Guide** (literature number SPRU137) describes how to install the TMS320C54x simulator and the C source debugger for the C54x. The installation for MS-DOS™, PC-DOS™, SunOS™, Solaris™, and HP-UX™ systems is covered.

- TMS320 Third-Party Support Reference Guide (literature number SPRU052) alphabetically lists over 100 third parties that provide various products that serve the family of TMS320 digital signal processors. A myriad of products and applications are offered—software and hardware development tools, speech recognition, image processing, noise cancellation, modems, etc.

TMS320 DSP Development Support Reference Guide (literature number SPRU011) describes the TMS320™ DSP family of digital signal processors and the tools that support these devices. Included are code-generation tools (compilers, assemblers, linkers, etc.) and system integration and debug tools (simulators, emulators, evaluation modules, etc.). Also covered are available documentation, seminars, the university program, and factory repair and exchange.

#### **Trademarks**

TMS320C54x, C54x, TMS320, ICECrusher, and MicroStar BGA are trademarks of Texas Instruments.

ARM7TDMI, ARM, Thumb, and Multi-ICE are registered trademarks of ARM Limited.

ICEBreaker, ARM7, and EmbeddedICE are trademarks of ARM Limited.

MS-DOS is a registered trademark of Microsoft Corporation.

OS/2 and PC-DOS are trademarks of International Business Machines Corporation.

SunOS and Solaris are trademarks of Sun Microsystems, Inc.

HP-UX is a trademark of Hewlett-Packard Company.

Other trademarks are the property of their respective owners.

# **Contents**

| 1 | Provi         | Introduction |                                                                                                                                                      |      |  |  |  |

|---|---------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|

|   | 1.1<br>1.2    |              | ral Description of the VC547xeatures of the VC547x                                                                                                   |      |  |  |  |

| 2 | Sumi<br>and A | marizes      | the TMS320VC547x architecture. Provides overview information about the res, and general information about the memory spaces, registers, and periphe. | DSP  |  |  |  |

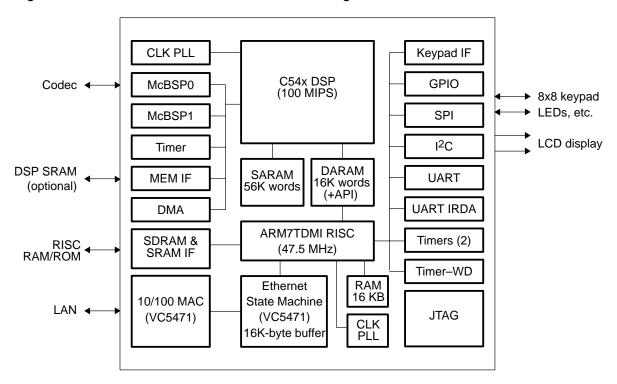

|   | 2.1           | Functi       | ional Overview of the VC547x                                                                                                                         | 2-2  |  |  |  |

|   | 2.2           | Functi       | ional Block Diagram of the VC547x                                                                                                                    | 2-4  |  |  |  |

|   | 2.3           |              | Subsystem Overview (TMS320C54x DSP Core)                                                                                                             | 2-5  |  |  |  |

|   |               | 2.3.1        | Features                                                                                                                                             |      |  |  |  |

|   |               | 2.3.2        | DSP CPU Core Associations                                                                                                                            |      |  |  |  |

|   | 2.4           |              | Memory Space                                                                                                                                         |      |  |  |  |

|   |               | 2.4.1        | On-Chip RAM                                                                                                                                          |      |  |  |  |

|   |               | 2.4.2        | Normal Mode DSP Memory Map                                                                                                                           |      |  |  |  |

|   |               | 2.4.3        | API Boot Mode                                                                                                                                        |      |  |  |  |

|   |               | 2.4.4        | API Boot Mode DSP Memory Map                                                                                                                         |      |  |  |  |

|   |               | 2.4.5        | Extended Program Memory                                                                                                                              |      |  |  |  |

|   |               | 2.4.6        | Relocatable Interrupt Vector Table                                                                                                                   |      |  |  |  |

|   | 2.5           |              | Registers                                                                                                                                            |      |  |  |  |

|   | 2.6           | DSP S        | Subsystem Peripherals                                                                                                                                |      |  |  |  |

|   |               | 2.6.1        | Multichannel Buffered Serial Ports (McBSP0 and McBSP1)                                                                                               |      |  |  |  |

|   |               | 2.6.2        | Direct Memory Access Controller (DMAC)                                                                                                               |      |  |  |  |

|   |               | 2.6.3        | ARM Port Interface (API)                                                                                                                             | 2-19 |  |  |  |

|   |               | 2.6.4        | Software-Programmable Wait-State Generator                                                                                                           | 2-19 |  |  |  |

|   |               | 2.6.5        | External Memory Interface                                                                                                                            | 2-20 |  |  |  |

|   |               | 2.6.6        | Hardware Timer                                                                                                                                       | 2-20 |  |  |  |

|   | 2.7           | ARM (        | Core Overview (ARM7TDMIE)                                                                                                                            | 2-21 |  |  |  |

|   |               | 2.7.1        | ARM7TDMI Overview                                                                                                                                    | 2-21 |  |  |  |

|   |               | 2.7.2        | ARM7TDMIE                                                                                                                                            |      |  |  |  |

|   |               | 2.7.3        | ARM7TDMIE Emulation Features                                                                                                                         | 2-22 |  |  |  |

|   | 2.8           | ARM N        | Memory Space                                                                                                                                         | 2-23 |  |  |  |

|   | 2.9  | ARM R     | Registers                                                                                                       | . 2-25 |

|---|------|-----------|-----------------------------------------------------------------------------------------------------------------|--------|

|   | 2.10 | ARM P     | Peripherals                                                                                                     | . 2-35 |

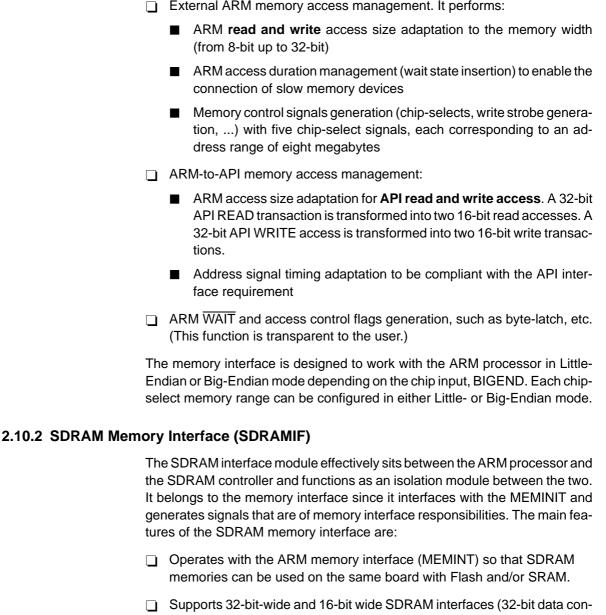

|   |      | 2.10.1    | ARM Memory Interface (MEMINT)                                                                                   | . 2-35 |

|   |      | 2.10.2    | SDRAM Memory Interface (SDRAMIF)                                                                                | . 2-35 |

|   |      | 2.10.3    | Interrupt Handler (INTH)                                                                                        | . 2-36 |

|   |      | 2.10.4    | ARM General-Purpose I/O (GPIO)                                                                                  | . 2-36 |

|   |      |           | Timers (TIMERs)                                                                                                 | . 2-38 |

|   |      | 2.10.6    | IRDA Universal Asynchronous Receiver/Transmitter 16C750 (UART-IRDA)                                             | . 2-38 |

|   |      | 2.10.7    | Universal Asynchronous Receiver/Transmitter 16C750 (UART-Modem)                                                 | . 2-39 |

|   |      | 2.10.8    | Serial Peripheral Interface (SPI)                                                                               | . 2-39 |

|   |      | 2.10.9    | Ethernet Interface Module (EIM) (VC5471)                                                                        | . 2-40 |

|   |      | 2.10.10   | Master Inter-Integrated Circuit (I <sup>2</sup> C) Interface                                                    | . 2-40 |

|   |      | 2.10.11   | Clock Management (CLKM)                                                                                         | . 2-41 |

|   | 2.11 | Genera    | al-Purpose Peripherals                                                                                          | . 2-42 |

|   | 2.12 | Clock F   | Frequencies                                                                                                     | . 2-43 |

|   |      | 2.12.1    | DSP Clock                                                                                                       | . 2-43 |

|   |      | 2.12.2    | ARM Clock                                                                                                       | . 2-44 |

|   |      | 2.12.3    | Audio Clock                                                                                                     | . 2-44 |

|   | 2.13 | Power-    | Down Modes                                                                                                      | . 2-45 |

|   |      | 2.13.1    | DSP Power-Down Modes                                                                                            | . 2-45 |

|   |      | 2.13.2    | ARM Power-Down Modes                                                                                            | . 2-46 |

|   | 2.14 |           | pt Management                                                                                                   |        |

|   |      | 2.14.1    | DSP Interrupts                                                                                                  | . 2-47 |

|   |      | 2.14.2    | MCU Interrupts                                                                                                  | . 2-48 |

| 3 | Memo | orv Inter | rface (MEMINT)                                                                                                  | 3-1    |

| - |      | -         | Nemory Interface function, discusses the System and API buses and the exteri                                    |        |

|   | memo | ory inter | face, provides an overview of SDRAM, and describes the SDRAM interfa<br>and its internal and external controls. |        |

|   | 3.1  | Memor     | y Interface (MEMINT) Function                                                                                   | 3-2    |

|   | 3.2  |           | n (Internal) Bus                                                                                                |        |

|   | 3.3  | ,         | s Interface                                                                                                     |        |

|   | 3.4  |           | al Memory Interface                                                                                             |        |

|   |      |           | ROM (Flash) and SRAM                                                                                            |        |

|   | 3.5  |           | ry Interface (MEMINT) Registers                                                                                 |        |

|   |      | 3.5.1     | External Memory Control Register for $\overline{\text{CS0}}$ – $\overline{\text{CS3}}$ , CS4 Memory Range       |        |

|   |      | 3.5.2     | ARM Port Interface Wait-State Configuration Register                                                            |        |

|   |      | 3.5.3     | API Control Register                                                                                            |        |

|   |      | 3.5.4     | Bank-Switching Control Register                                                                                 |        |

|   |      | 3.5.5     | SDRAM Data Bus Size Control Register                                                                            |        |

|   |      | 3.5.6     | Bank-Switching Configuration Register                                                                           |        |

|   | 3.6  |           | Memory Space                                                                                                    |        |

|   | 3.7                                                                                                                                                                                                                              | SDRAN   | Λ 3-2                                                                                                                            | 5 |  |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------|---|--|

|   |                                                                                                                                                                                                                                  | 3.7.1   | Introduction                                                                                                                     | 5 |  |

|   |                                                                                                                                                                                                                                  | 3.7.2   | SDRAM IF Overview                                                                                                                | 6 |  |

|   |                                                                                                                                                                                                                                  | 3.7.3   | Supported Devices                                                                                                                |   |  |

|   | 3.8                                                                                                                                                                                                                              | SDRAN   | # Interface                                                                                                                      |   |  |

|   | 3.9                                                                                                                                                                                                                              | SDRAN   | ## IF Registers 3-2                                                                                                              | 9 |  |

|   |                                                                                                                                                                                                                                  | 3.9.1   | SDRAM Configuration Register 3-3                                                                                                 | 0 |  |

|   |                                                                                                                                                                                                                                  | 3.9.2   | SDRAM Refresh Counter Register                                                                                                   |   |  |

|   |                                                                                                                                                                                                                                  | 3.9.3   | SDRAM Control Register                                                                                                           | 5 |  |

|   |                                                                                                                                                                                                                                  | 3.9.4   | SDRAM Initialization Refresh Counter Register                                                                                    | 6 |  |

|   | 3.10                                                                                                                                                                                                                             | Wavefo  | orms 3-3                                                                                                                         | 7 |  |

|   |                                                                                                                                                                                                                                  | 3.10.1  | Waveforms of Read/Write Operations With Rows Enabled/Disabled 3-3                                                                | 7 |  |

|   |                                                                                                                                                                                                                                  | 3.10.2  | Waveforms With External Transactions (8-, 16-, and 32-Bit Devices) 3-4                                                           | 1 |  |

| 4 | Interr                                                                                                                                                                                                                           | upt Han | dler 4-                                                                                                                          | 1 |  |

|   |                                                                                                                                                                                                                                  |         | ectional description of the Interrupt Handler, describes the microcontroller (MCU) ests, and shows the MCU accessible registers. |   |  |

|   | 4.1                                                                                                                                                                                                                              | Functio | nal Description                                                                                                                  | 2 |  |

|   | 4.2                                                                                                                                                                                                                              | MCU Ir  | nterrupts                                                                                                                        | 3 |  |

|   |                                                                                                                                                                                                                                  | 4.2.1   | Internal Registers 4-                                                                                                            | 5 |  |

|   |                                                                                                                                                                                                                                  | 4.2.2   | Interrupt Sequence 4-                                                                                                            | 6 |  |

|   | 4.3                                                                                                                                                                                                                              | ARM M   | lemory-Mapped Registers4-                                                                                                        | 7 |  |

|   |                                                                                                                                                                                                                                  | 4.3.1   | Interrupt Register 4-                                                                                                            | 8 |  |

|   |                                                                                                                                                                                                                                  | 4.3.2   | Mask Interrupt Register 4-1                                                                                                      | 0 |  |

|   |                                                                                                                                                                                                                                  | 4.3.3   | Source IRQ Register 4-1                                                                                                          | 1 |  |

|   |                                                                                                                                                                                                                                  | 4.3.4   | Source FIQ Register 4-1                                                                                                          | 2 |  |

|   |                                                                                                                                                                                                                                  | 4.3.5   | Interrupt Control Register                                                                                                       | 3 |  |

|   |                                                                                                                                                                                                                                  | 4.3.6   | IRQ Sleep Register 4-1                                                                                                           | 3 |  |

|   |                                                                                                                                                                                                                                  | 4.3.7   | Interrupt Level Registers (Read/Write)                                                                                           | 4 |  |

|   |                                                                                                                                                                                                                                  | 4.3.8   | Interrupt Level Register 0                                                                                                       | 5 |  |

| 5 |                                                                                                                                                                                                                                  | _       | ement Module                                                                                                                     | 1 |  |

|   | Provides an overview of the clock management module, describes the three modes of clock operation for both the DSP and ARM subsystems, shows the clock module registers, and discusses the phase-locked loop (PLL) clock source. |         |                                                                                                                                  |   |  |

|   | 5.1                                                                                                                                                                                                                              | Clock N | Management Module Overview 5-                                                                                                    | 2 |  |

|   |                                                                                                                                                                                                                                  | 5.1.1   | Clock Operation Modes 5-                                                                                                         | 2 |  |

|   |                                                                                                                                                                                                                                  | 5.1.2   | Features Controlled by the Clock Management Module 5-                                                                            |   |  |

|   | 5.2                                                                                                                                                                                                                              | Clock N | Module Register Tables 5-                                                                                                        |   |  |

|   |                                                                                                                                                                                                                                  | 5.2.1   | CLKM Module Registers 5-                                                                                                         | 5 |  |

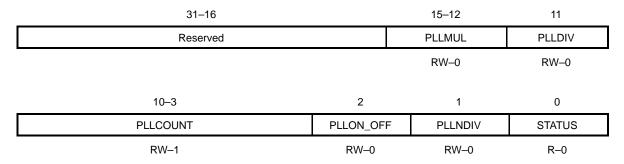

|   |                                                                                                                                                                                                                                  | 5.2.2   | PLL_REG Register (ARMSS) 5-                                                                                                      |   |  |

|   |                                                                                                                                                                                                                                  | 5.2.3   | CLKMD Register (DSPSS)                                                                                                           |   |  |

|   | 5.3                                                                                          | DSP Subsystem Control                                                                              | 5-7             |  |  |  |

|---|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------|--|--|--|

|   |                                                                                              | 5.3.1 DSP Phase-Locked Loop Register                                                               | 5-7             |  |  |  |

|   |                                                                                              | 5.3.2 Reset Control Register                                                                       | 5-10            |  |  |  |

|   | 5.4                                                                                          | ARM Subsystem Control                                                                              | 5-11            |  |  |  |

|   |                                                                                              | 5.4.1 Clock Configuration Register                                                                 | 5-11            |  |  |  |

|   |                                                                                              | 5.4.2 Interrupt Clock Wakeup Register                                                              | 5-13            |  |  |  |

|   |                                                                                              | 5.4.3 Reset Register                                                                               | 5-15            |  |  |  |

|   |                                                                                              | 5.4.4 Audio Rate Register                                                                          |                 |  |  |  |

|   |                                                                                              | 5.4.5 Watchdog Status Register                                                                     |                 |  |  |  |

|   |                                                                                              | 5.4.6 Low-Power Mode Register                                                                      |                 |  |  |  |

|   |                                                                                              | 5.4.7 Low-Power Register Value Register                                                            |                 |  |  |  |

|   | 5.5                                                                                          | Phase-Locked Loop (PLL)                                                                            |                 |  |  |  |

|   |                                                                                              | 5.5.1 PLL_REG Register (ARMSS)                                                                     |                 |  |  |  |

|   |                                                                                              | 5.5.2 CLKMD Clock Control Register (DSPSS)                                                         | 5-25            |  |  |  |

| 6 | Time                                                                                         | er Module                                                                                          | 6-1             |  |  |  |

|   |                                                                                              | vides a description of the three timers implemented on the TMS320VC5                               |                 |  |  |  |

|   |                                                                                              | ses the watchdog function, and shows the timer registers.                                          | TIX dovice, ale |  |  |  |

|   | 6.1                                                                                          | Timer Module Introduction                                                                          | 6-2             |  |  |  |

|   | 6.2                                                                                          | TIMER0                                                                                             |                 |  |  |  |

|   | 0.2                                                                                          | 6.2.1 Disabling the Watchdog Function                                                              |                 |  |  |  |

|   |                                                                                              | 6.2.2 Re-Enabling the Watchdog Function                                                            |                 |  |  |  |

|   |                                                                                              | 6.2.3 Timer0 Control Register                                                                      |                 |  |  |  |

|   |                                                                                              | 6.2.4 Timer0 Current Value Register                                                                |                 |  |  |  |

|   | 6.3                                                                                          | TIMER1 and TIMER2                                                                                  |                 |  |  |  |

|   |                                                                                              | 6.3.1 Timer Interrupt Period                                                                       |                 |  |  |  |

|   |                                                                                              | 6.3.2 TIMER1 and TIMER2 Control Registers                                                          |                 |  |  |  |

|   |                                                                                              | 6.3.3 TIMER1 and TIMER2 Current Value Registers                                                    |                 |  |  |  |

|   | 6.4                                                                                          | Programming the Timers                                                                             |                 |  |  |  |

|   | 6.5                                                                                          | Read Timer Operations                                                                              | 6-10            |  |  |  |

| 7 | Gono                                                                                         | neral-Purpose I/O Module (GPIO)                                                                    | 7.1             |  |  |  |

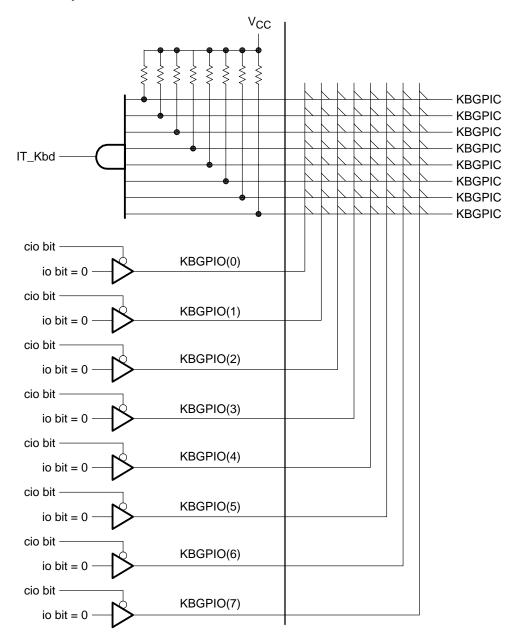

| ′ |                                                                                              | vides a functional description of the general-purpose I/O module (GPIC                             |                 |  |  |  |

|   |                                                                                              | vides a functional description of the general-purpose 1/O module (GFTC<br>IO and KBGPIO registers. | ) and snows an  |  |  |  |

|   |                                                                                              | _                                                                                                  | 7.0             |  |  |  |

|   | 7.1                                                                                          | Functional Description                                                                             |                 |  |  |  |

|   | 7.2                                                                                          | 7.1.1 General-Purpose I/O (GPIO)                                                                   |                 |  |  |  |

|   | 1.2                                                                                          | 7.2.1 GPIO Registers                                                                               |                 |  |  |  |

|   |                                                                                              | 7.2.1 GFIO Registers                                                                               |                 |  |  |  |

|   |                                                                                              | 7.2.3 Keyboard Connection                                                                          |                 |  |  |  |

|   | 7.3                                                                                          | Input/Outputs of GPIO Module                                                                       |                 |  |  |  |

|   |                                                                                              |                                                                                                    |                 |  |  |  |

| 8 |                                                                                              | RT IRDA Module                                                                                     |                 |  |  |  |

|   | Explains the features of the UART IRDA module, shows the applicable registers, and discusses |                                                                                                    |                 |  |  |  |

|   |                                                                                              | serial infrared (SIR) mode and the universal asynchronous receiver/trail                           | nsmitter (UART) |  |  |  |

|   | mode                                                                                         |                                                                                                    |                 |  |  |  |

|   | 8.1                                                                                          | General Description                                                                                | 8-2             |  |  |  |

| 8.2 | Main F  | eatures                                        | . 8-3 |

|-----|---------|------------------------------------------------|-------|

|     | 8.2.1   | UART Mode Features                             | . 8-3 |

|     | 8.2.2   | IrDA SIR Mode Features                         | . 8-4 |

| 8.3 | I/O Des | scription                                      | . 8-5 |

| 8.4 | Registe | er Mapping/Descriptions                        | . 8-6 |

|     | 8.4.1   | UART IRDA Module Registers                     | . 8-6 |

|     | 8.4.2   | Special Access Registers                       | . 8-8 |

|     | 8.4.3   | Register Mapping                               | . 8-8 |

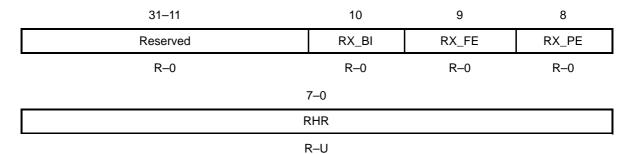

|     | 8.4.4   | Receive Holding Register                       | . 8-9 |

|     | 8.4.5   | Transmit Holding Register                      | 8-10  |

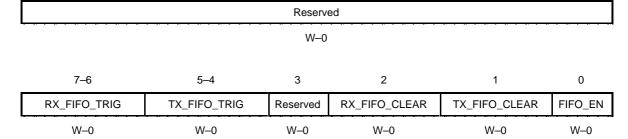

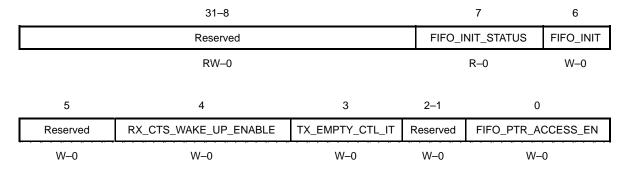

|     | 8.4.6   | FIFO Control Register                          | 8-11  |

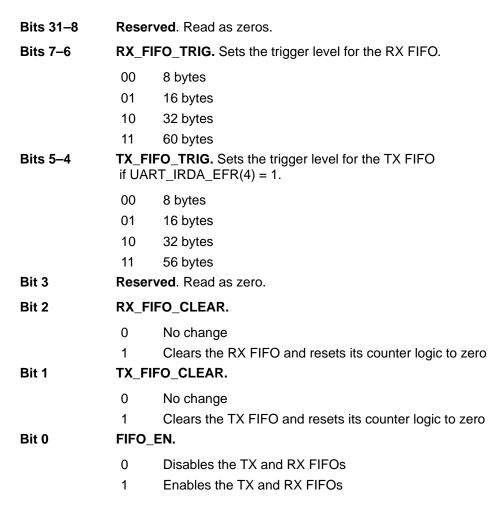

|     | 8.4.7   | Status Control Register                        | 8-12  |

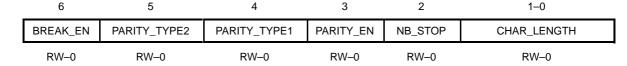

|     | 8.4.8   | Line Control Register (UART Mode Only)         | 8-14  |

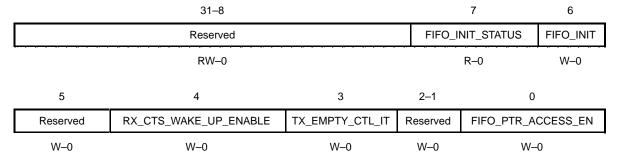

|     | 8.4.9   | Line Status Register                           |       |

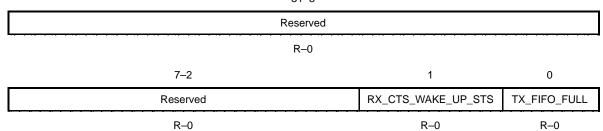

|     | 8.4.10  | Supplementary Status Register                  | 8-18  |

|     | 8.4.11  | Modem Control Register                         | 8-18  |

|     | 8.4.12  | Modem Status Register                          | 8-19  |

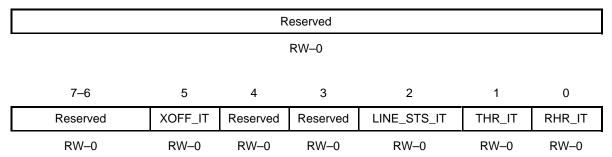

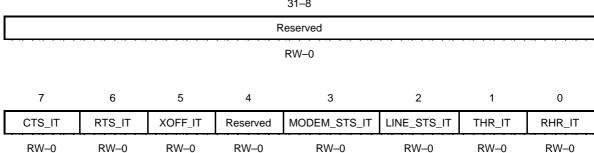

|     | 8.4.13  | Interrupt Enable Register                      | 8-20  |

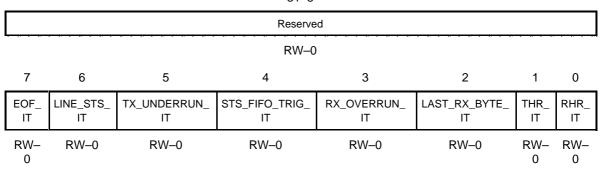

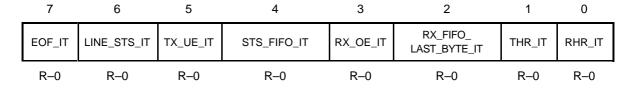

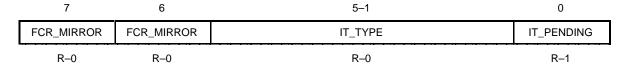

|     | 8.4.14  | Interrupt Status Register                      | 8-22  |

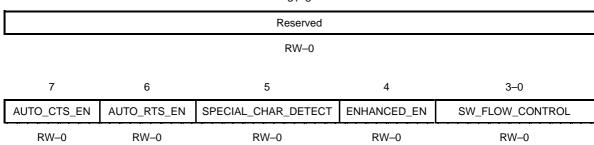

|     | 8.4.15  | Enhanced Feature Register                      | 8-24  |

|     | 8.4.16  | XON1 Character Register                        | 8-26  |

|     | 8.4.17  | XON2 Character Register                        | 8-26  |

|     | 8.4.18  | XOFF1 Character Register                       | 8-27  |

|     |         | XOFF2 Character Register                       |       |

|     | 8.4.20  | Scratch Pad Register                           | 8-28  |

|     | 8.4.21  | Divisor for 115K-Baud Generation Register      | 8-28  |

|     |         | Divisor for Baud-Rate Generation Register      |       |

|     | 8.4.23  | Transmission Control Register (UART Mode Only) | 8-30  |

|     |         | Trigger Level Register                         |       |

|     |         | Mode Definition Register 1                     |       |

|     | 8.4.26  | Mode Definition Register 2                     | 8-33  |

|     | 8.4.27  | Transmit Frame Length Register (LSB)           | 8-34  |

|     | 8.4.28  | Transmit Frame Length Register (MSB)           | 8-34  |

|     |         | Receive Frame Length Register (LSB)            |       |

|     |         | Receive Frame Length Register (MSB)            |       |

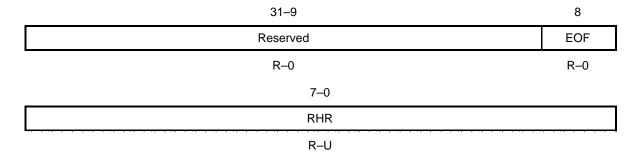

|     | 8.4.31  | Status FIFO Line Status Register               | 8-36  |

|     |         | Status FIFO Register                           |       |

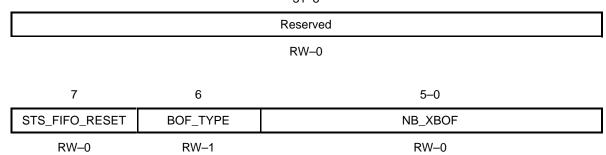

|     |         | Beginning-of-File Length Register              |       |

|     |         | Pulse Width Register                           |       |

|     |         | Auxiliary Control Register                     |       |

|     |         | Start Point for IR Transmission                |       |

|     |         | Access to Read and Write Pointers              |       |

|     |         | Resume Register                                |       |

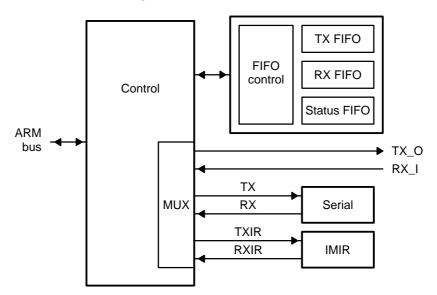

| 8.5 | UART I  | IRDA Functional Block Diagram                  | 8-45  |

|   | 8.6 | Serial I | Infrared Mode and Protocol 8-4                                                       | 46 |

|---|-----|----------|--------------------------------------------------------------------------------------|----|

|   |     | 8.6.1    | CRC Generation 8-4                                                                   | 47 |

|   |     | 8.6.2    | Asynchronous Transparency 8-4                                                        | 47 |

|   |     | 8.6.3    | Abort Sequence 8-4                                                                   | 48 |

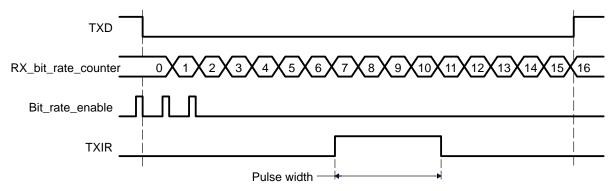

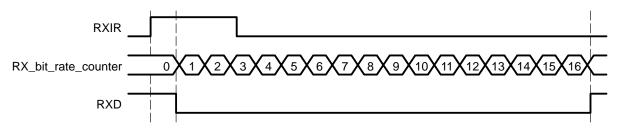

|   |     | 8.6.4    | Pulse Shaping 8-4                                                                    | 48 |

|   |     | 8.6.5    | Address Checking 8-5                                                                 | 51 |

|   | 8.7 | Function | onal Descriptions 8-5                                                                | 52 |

|   |     | 8.7.1    | Trigger Levels 8-5                                                                   | 52 |

|   |     | 8.7.2    | Interrupts                                                                           |    |

|   |     | 8.7.3    | Features Available in UART Mode 8-5                                                  | 54 |

|   |     | 8.7.4    | Features Available in SIR Mode 8-5                                                   | 56 |

| 9 | UAR | Γ Moden  | n Interface 9                                                                        | -1 |

| • |     |          | features of the UART Modem module, shows the applicable registers, and pro-          | •  |

|   | •   |          | onal description that includes trigger levels, interrupts, break and time-out condi- |    |

|   |     |          | re and software flow control, and the Autobauding mode.                              |    |

|   | 9.1 | Genera   | al Description                                                                       | -2 |

|   | 9.2 | Main F   | eatures                                                                              | -2 |

|   |     | 9.2.1    | UART Mode Features 9                                                                 | -3 |

|   | 9.3 | I/O Des  | scription 9                                                                          | -4 |

|   | 9.4 | Registe  | er Mapping/Descriptions 9                                                            | -5 |

|   |     | 9.4.1    | UART Modem Module Registers 9                                                        | -5 |

|   |     | 9.4.2    | Special Access Registers 9                                                           | -6 |

|   |     | 9.4.3    | Receive Holding Register                                                             | -6 |

|   |     | 9.4.4    | Transmit Holding Register 9                                                          | -8 |

|   |     | 9.4.5    | FIFO Control Register                                                                | -9 |

|   |     | 9.4.6    | Status Control Register                                                              | 10 |

|   |     | 9.4.7    | Line Control Register 9-                                                             | 11 |

|   |     | 9.4.8    | Line Status Register 9-7                                                             | 13 |

|   |     | 9.4.9    | Supplementary Status Register                                                        | 14 |

|   |     | 9.4.10   | Modem Control Register                                                               | 15 |

|   |     | 9.4.11   | Modem Status Register                                                                | 16 |

|   |     | 9.4.12   | Interrupt Enable Register 9-7                                                        | 17 |

|   |     | 9.4.13   | Interrupt Status Register                                                            | 18 |

|   |     | 9.4.14   | Enhanced Feature Register 9-7                                                        | 19 |

|   |     | 9.4.15   | XON1 Character Register 9-2                                                          | 21 |

|   |     | 9.4.16   | XON2 Character Register 9-2                                                          | 21 |

|   |     | 9.4.17   | XOFF1 Character Register 9-2                                                         | 22 |

|   |     | 9.4.18   | XOFF2 Character Register 9-2                                                         | 22 |

|   |     | 9.4.19   | Scratch-Pad Register 9-2                                                             | 23 |

|   |     | 9.4.20   | Divisor for 115k-Baud Generation                                                     | 23 |

|   |     | 9.4.21   | Divisor for Baud-Rate Generation                                                     | 24 |

|   |     | 9.4.22   | Transmission Control Register 9-2                                                    | 25 |

|   |     | 9.4.23   | Trigger-Level Register 9-2                                                           | 26 |

|   |     |          |                                                                                      |    |

|     |        | 9.4.24                 | Mode Definition Register                                                           | 9-27      |

|-----|--------|------------------------|------------------------------------------------------------------------------------|-----------|

|     |        | 9.4.25                 | UART Autobauding Status Register                                                   | 9-28      |

|     |        | 9.4.26                 | RX FIFO Read Pointer Register                                                      | 9-29      |

|     |        | 9.4.27                 | RX FIFO Write Pointer Register                                                     | 9-30      |

|     |        | 9.4.28                 | TX FIFO Read Pointer Register                                                      | 9-30      |

|     |        | 9.4.29                 | TX FIFO Write Pointer Register                                                     | 9-31      |

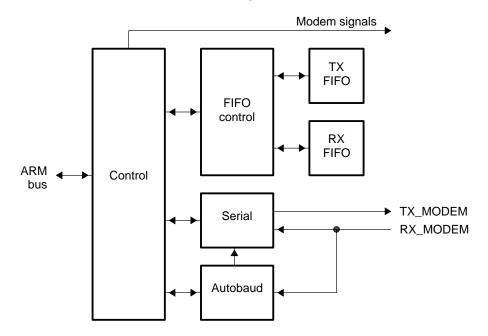

|     | 9.5    | Functio                | onal Block Diagram                                                                 | 9-32      |

|     | 9.6    | Functio                | onal Descriptions                                                                  | 9-33      |

|     |        | 9.6.1                  | Trigger Levels                                                                     | 9-33      |

|     |        | 9.6.2                  | Interrupts                                                                         |           |

|     |        | 9.6.3                  | Break and Time-Out Conditions                                                      | 9-34      |

|     |        | 9.6.4                  | Hardware Flow Control                                                              |           |

|     |        | 9.6.5                  | Software Flow Control                                                              |           |

|     |        | 9.6.6                  | Autobauding Mode                                                                   | 9-36      |

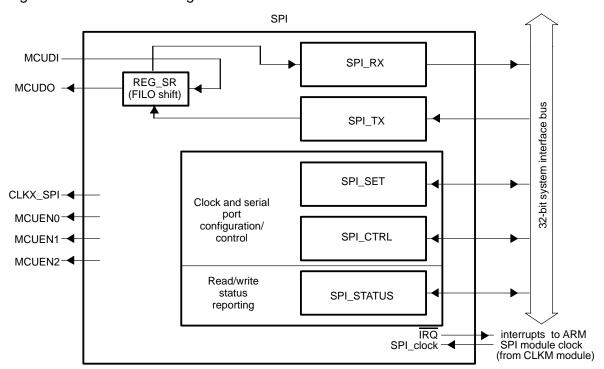

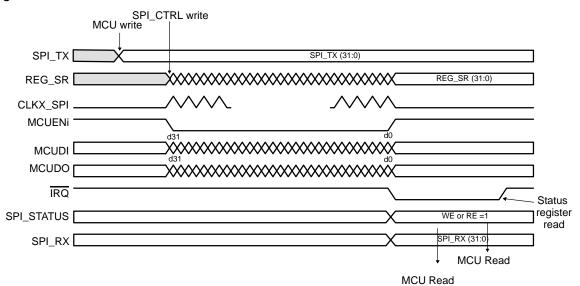

| 10  | Serial | Port In                | terface (SPI)                                                                      | 10-1      |

| . • |        |                        | operation of the serial port interfce (SPI) and includes register defir            |           |

|     |        | diagran                |                                                                                    |           |

|     | 10.1   | SPI Ma                 | in Features                                                                        | 10-2      |

|     | 10.2   | SPI Ge                 | neral Description                                                                  | 10-2      |

|     | 10.3   | SPI I/O                | Description                                                                        | 10-4      |

|     | 10.4   | SPI Re                 | gisters                                                                            | 10-5      |

|     |        |                        | SPI Setup Register                                                                 |           |

|     |        |                        | SPI Control Register                                                               |           |

|     |        |                        | SPI Status Register                                                                |           |

|     |        |                        | SPI Transmit Register                                                              |           |

|     |        |                        | SPI Receive Register                                                               |           |

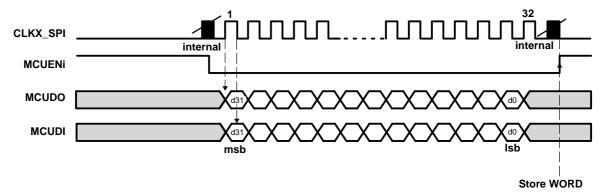

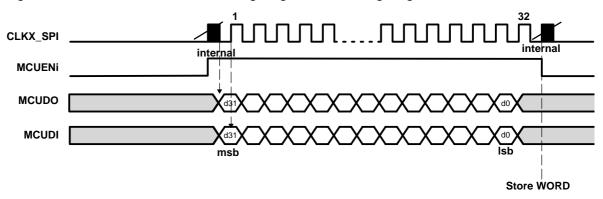

|     | 10.5   |                        | otocol Description                                                                 |           |

|     |        | 10.5.1                 | Transmit Protocol                                                                  |           |

|     |        |                        | Receive Protocol                                                                   |           |

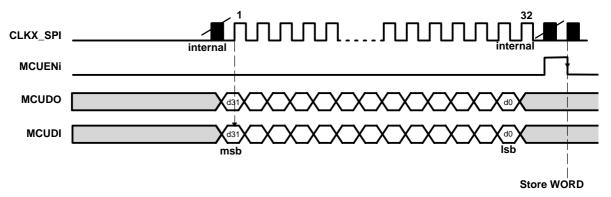

|     |        | 10.5.3                 | Transmission Mode Waveforms                                                        | 10-12     |

| 11  | Maste  | er I <sup>2</sup> C In | terface                                                                            | 11-1      |

|     |        |                        | neral description of the $I^2C$ Interface, shows the applicable registers,         |           |

|     |        |                        | otocol and Master I <sup>2</sup> C interface resets, and discusses interrupt, FIFO | and clock |

|     |        | gement.                |                                                                                    |           |

|     | 11.1   |                        | I <sup>2</sup> C Interface Module General Description                              |           |

|     |        |                        | Overview                                                                           |           |

|     |        |                        | Main Features                                                                      |           |

|     |        |                        | Special Considerations                                                             |           |

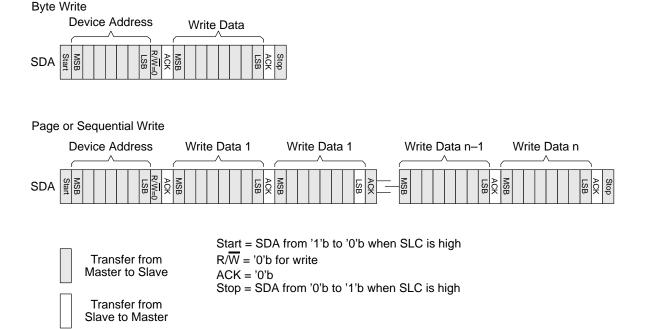

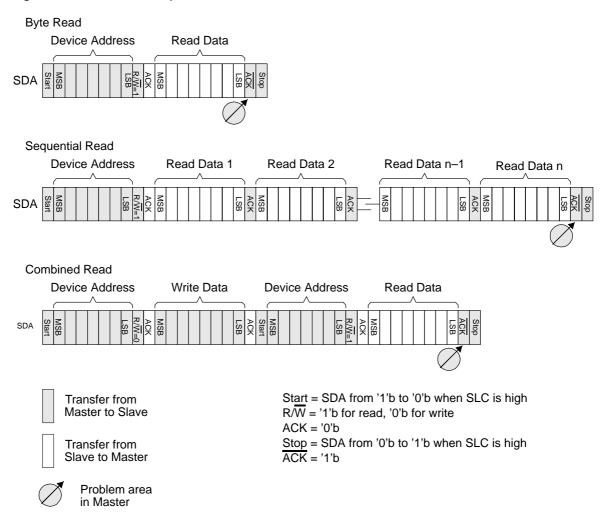

|     |        |                        | Standard I <sup>2</sup> C Bus Protocol                                             |           |

|     | 11.2   | I/O Des                | scription                                                                          | 11-8      |

|    | 11.3  | Registe  | er Descriptions                                                    | . 11-9 |

|----|-------|----------|--------------------------------------------------------------------|--------|

|    |       | 11.3.1   | Device Register                                                    | 11-10  |

|    |       | 11.3.2   | Address Register                                                   | 11-10  |

|    |       | 11.3.3   | Data Write Register                                                | 11-11  |

|    |       | 11.3.4   | Data Read Register                                                 | 11-11  |

|    |       | 11.3.5   | Command Register                                                   | 11-12  |

|    |       | 11.3.6   | Configuration FIFO Register                                        | 11-13  |

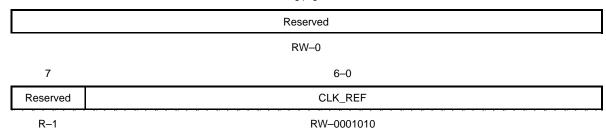

|    |       | 11.3.7   | Configuration Clock Register                                       | 11-13  |

|    |       | 11.3.8   | Configuration Clock Functional Reference Register                  | 11-14  |

|    |       |          | Status FIFO Register                                               |        |

|    |       | 11.3.10  | Status Activity Register                                           | 11-16  |

|    | 11.4  |          | lanagement                                                         |        |

|    | 11.5  |          | I <sup>2</sup> C Interface Resets                                  |        |

|    | 11.6  |          | Management                                                         |        |

|    | 11.7  | Interrup | ot Management                                                      | 11-18  |

| 12 | Fther | net Inte | rface Module (EIM)                                                 | 12-1   |

| 12 |       |          | Ethernet interface module (EIM), its registers, and its operation. | . 12-1 |

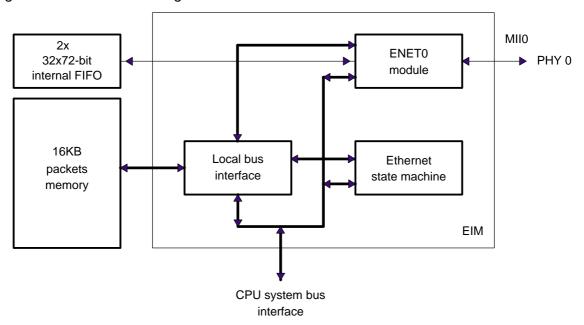

|    | 12.1  |          | verview                                                            | 12-2   |

|    | 12.1  |          | General Description                                                |        |

|    | 12.2  |          | et Interface Signals                                               |        |

|    | 12.3  |          | Functional Description                                             |        |

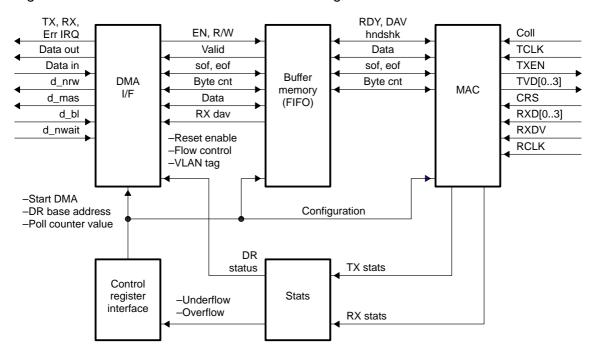

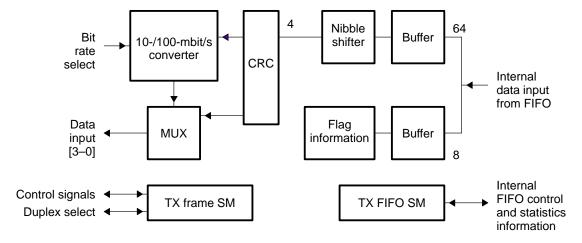

|    | 12.0  | 12.3.1   |                                                                    |        |

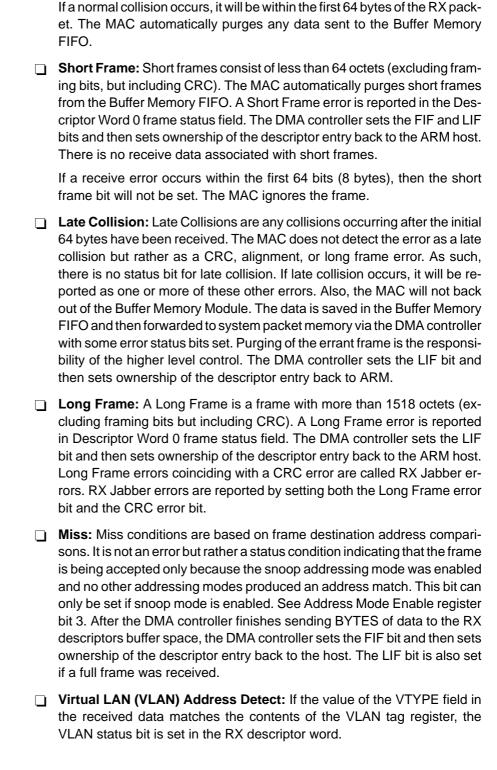

|    |       |          | Buffer Memory Unit (FIFO)                                          |        |

|    |       |          | DMA Controller                                                     |        |

|    |       |          | Control Registers Interface                                        |        |

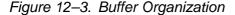

|    |       |          | Media Access Controller (MAC)                                      |        |

|    |       |          | Statistics Block                                                   |        |

|    |       | 12.3.7   | Loopback                                                           |        |

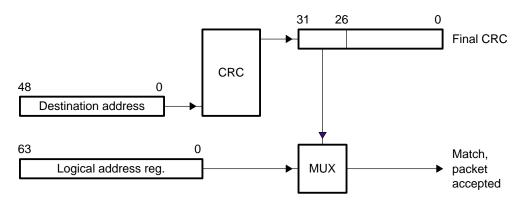

|    |       | 12.3.8   | ·                                                                  |        |

|    |       | 12.3.9   | Addressing Modes                                                   |        |

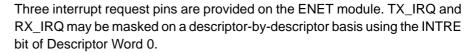

|    |       |          | ENET Interrupts                                                    |        |

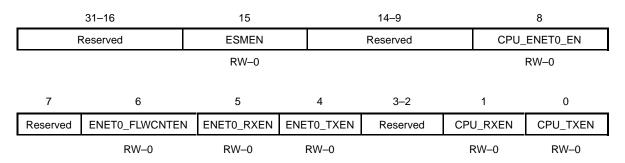

|    |       |          | Configuration                                                      |        |

|    | 12.4  | EIM De   | escriptors Structure                                               | 12-22  |

|    |       | 12.4.1   | TX Descriptor Ring                                                 | 12-22  |

|    |       | 12.4.2   | RX Descriptor Ring                                                 | 12-26  |

|    | 12.5  | EIM Pe   | ripheral Register Tables                                           | 12-29  |

|    | 12.6  |          | eripheral Registers                                                |        |

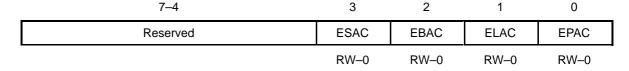

|    |       | 12.6.1   | EIM ESM Control Register                                           | 12-32  |

|    |       |          | EIM ESM Status Register                                            |        |

|    |       |          | EIM CPU TX Descriptors Base Address Register                       |        |

|    |       |          | EIM CPU RX Descriptors Base Address Register                       |        |

|    |       |          | EIM Packet Buffer Size Register                                    |        |

|    |       | 1266     | FIM CPLI Filtering Control Register                                | 12-37  |

|      | 12.6.7 EIM CPU Destination Address Register, High Word                   | 12-38 |

|------|--------------------------------------------------------------------------|-------|

|      | 12.6.8 EIM CPU Destination Address Register, Low Word                    | 12-38 |

|      | 12.6.9 EIM Multicast Filter Valid Register, High Word                    | 12-39 |

|      | 12.6.10 EIM Multicast Filter Valid Register, Low Word                    | 12-39 |

|      | 12.6.11 EIM Multicast Filter Mask Register, High Word                    | 12-40 |

|      | 12.6.12 EIM Multicast Filter Mask Register, Low Word                     | 12-40 |

|      | 12.6.13 EIM RX Threshold Register                                        |       |

|      | 12.6.14 EIM CPU RX Ready Register                                        |       |

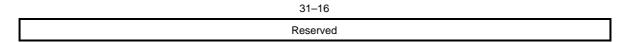

|      | 12.6.15 EIM ESM Interrupt Enable Register                                |       |

|      | 12.6.16 EIM ENET0 TX Queue Current Pointer Register                      | 12-43 |

|      | 12.6.17 EIM ENETO RX Queue Current Pointer Register                      | 12-44 |

|      | 12.6.18 EIM CPU TX Queue Current Pointer Register                        |       |

|      | 12.6.19 EIM CPU RX Queue Current Pointer Register                        |       |

| 12.7 | ENET0 Registers                                                          |       |

|      | 12.7.1 EIM ENET0 Mode Register                                           |       |

|      | 12.7.2 EIM ENET0 Backoff Seed Register                                   |       |

|      | 12.7.3 EIM ENET0 Backoff Count Register                                  |       |

|      | 12.7.4 EIM ENET0 TX Flow Pause Count Register                            | 12-50 |

|      | 12.7.5 EIM ENET0 Flow Control Register                                   |       |

|      | 12.7.6 EIM ENET0 VTYPE Tag Register                                      |       |

|      | 12.7.7 EIM ENETO System Error Interrupt Status Register                  |       |

|      | 12.7.8 EIM ENET0 Transmit Descriptor Buffer Ready Register               |       |

|      | 12.7.9 EIM ENET0 Transmit Descriptor Base Address Register               |       |

|      | 12.7.10 EIM ENETO Receive Descriptor Base Address Register               |       |

|      | 12.7.11 EIM ENET0 Destination Physical Address Match Register, High Word | 12-55 |

|      | 12.7.12 EIM ENET0 Destination Physical Address Match Register, Low Word  | 12-56 |

|      | 12.7.13 EIM ENET0 Logical Address Hash Filter Register, High Word        | 12-56 |

|      | 12.7.14 EIM ENET0 Logical Address Hash Filter Register, Low Word         |       |

|      | 12.7.15 EIM ENETO Address Mode Enable Register                           |       |

|      | 12.7.16 EIM ENETO Descriptor Ring Poll Interval Count Register           |       |

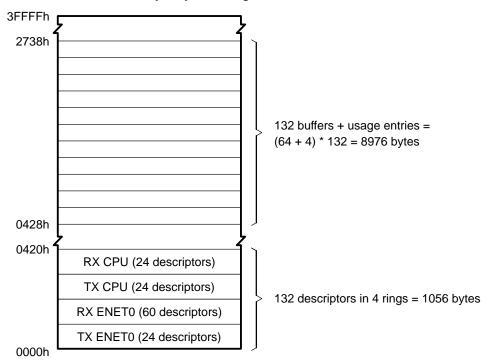

| 12.8 | EIM Packet RAM Structure                                                 | 12-59 |

|      | 12.8.1 Logical Organization                                              | 12-59 |

|      | 12.8.2 Packets Memory Physical Organization                              | 12-60 |

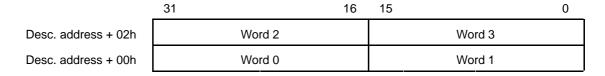

|      | 12.8.3 Descriptor Words                                                  |       |

|      | 12.8.4 CPU TX Descriptor                                                 | 12-61 |

|      | 12.8.5 CPU RX Descriptor                                                 | 12-62 |

|      | 12.8.6 ENET0 RX Descriptors                                              | 12-63 |

|      | 12.8.7 ENET0 TX Descriptors                                              |       |

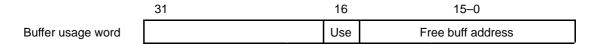

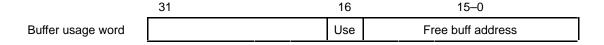

|      | 12.8.8 Buffer Usage Word                                                 |       |

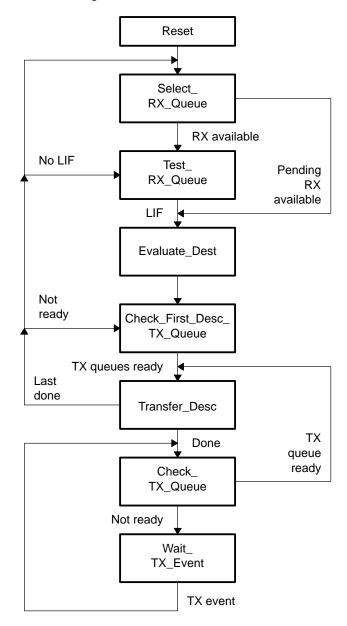

| 12.9 | EIM ESM Functional Description                                           |       |

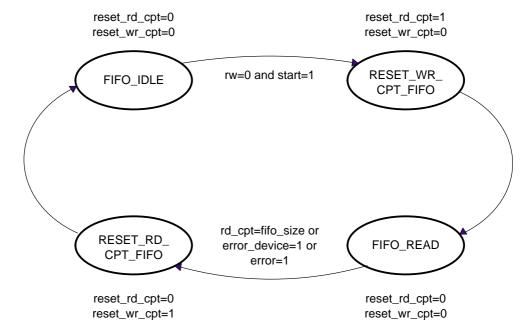

|      | 12.9.1 Main State Machine Description                                    |       |

|      | 12.9.2 Reset State                                                       |       |

|      | 12.9.3 Select_RX_Queue State                                             |       |

|      | 12.9.4 Test RX Queue State                                               |       |

|    |         | 12.9.5    | Evaluate_Dest State                                        | 12-70  |

|----|---------|-----------|------------------------------------------------------------|--------|

|    |         | 12.9.6    | Check_First_Desc_TX_Queue State                            | 12-70  |

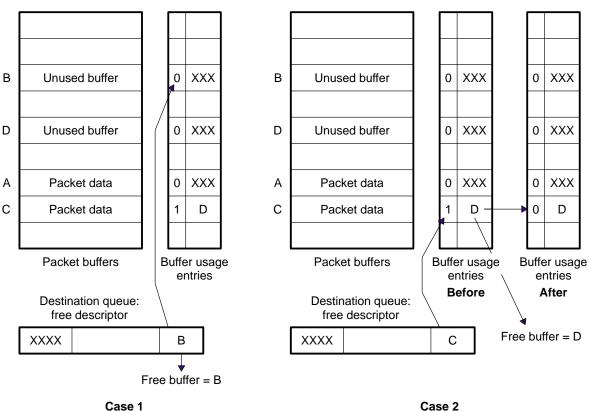

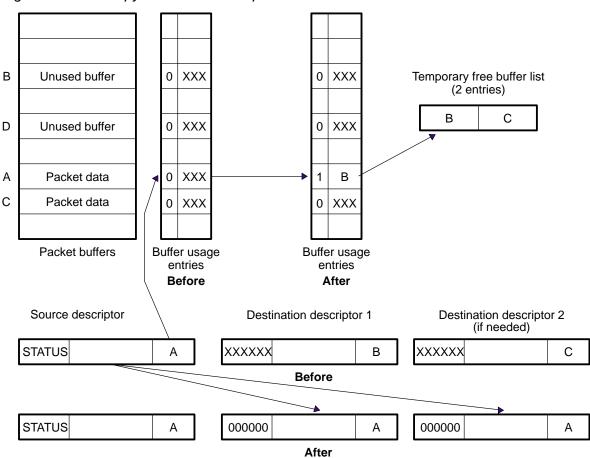

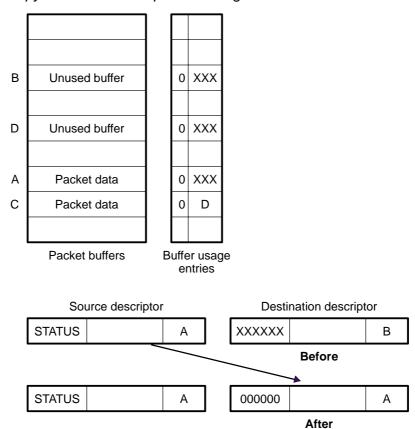

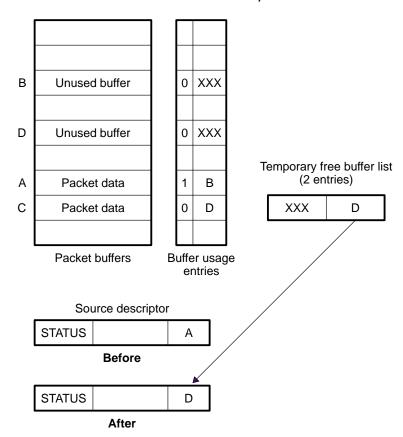

|    |         | 12.9.7    | Transfer_Desc State                                        | 12-71  |

|    |         | 12.9.8    | Check_TX_Queue State                                       | 12-76  |

|    |         | 12.9.9    | Wait_TX_Event State                                        | 12-76  |

|    | 12.10   | EIM Op    | peration                                                   | 12-77  |

|    |         | 12.10.1   | Setting Up                                                 | 12-77  |

|    |         | 12.10.2   | Packets Operation                                          | 12-78  |

|    | 12.11   | ENET (    | Operation                                                  | 12-80  |

|    |         | 12.11.1   | Setting Up                                                 | 12-80  |

|    |         | 12.11.2   | Packet Operations                                          | 12-80  |

| 13 | Initial | ization   | Protocol                                                   | . 13-1 |

|    |         |           | ware logic reset, ARM code downloading, and DSP boot mode. |        |

|    | 13.1    | Initializ | ation Protocol                                             | . 13-2 |

|    |         | 13.1.1    | Hardware Logic Reset                                       | . 13-2 |

|    |         | 13.1.2    | ARM Code Downloading                                       | . 13-2 |

|    |         | 13.1.3    | DSP Boot Mode                                              | 13-3   |

# **Figures**

| 2–1  | TMS320VC547x Functional Block Diagram                                                       | 2-4  |

|------|---------------------------------------------------------------------------------------------|------|

| 2–2  | DSP Subsystem Memory Map for DSP Accesses (When DSP_APIBN = 1 or ABMDIS = 1)                | 2-8  |

| 2–3  | API Boot Mode DSP Subsystem Memory Map for DSP Accesses (When DSP_APIBN = 0 and ABMDIS = 0) |      |

| 2–4  | DSP Extended Program Memory Map                                                             |      |

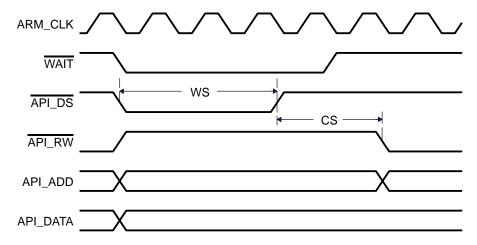

| 3–1  | 16-Bit API Write Access With API_WS = 3, API_CS = 2, API_BS = 1                             |      |

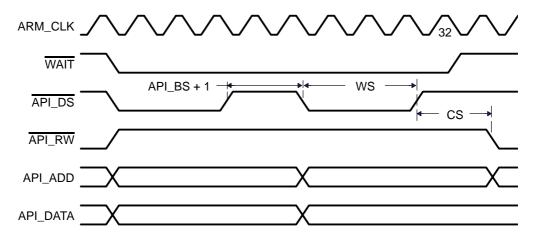

| 3–2  | 32-Bit API Write Access with API_WS = 3, API_CS = 2, API_BS = 1                             |      |

| 3–3  | External Memory Control Register for CS0–CS3, CS4 Memory Range (CS0_REG–CS4_REG)            |      |

| 3–4  | ARM Port Interface Wait-State Configuration Register (API_REG)                              |      |

| 3–5  | API Control Register (APIC)                                                                 |      |

| 3–6  | Bank-Switching Control Register (BSCR)                                                      |      |

| 3–7  | SDRAM Data Bus Size Control Register (SDRAM_REG)                                            |      |

| 3–8  | Bank-Switching Configuration Register (BS_CONFIG)                                           | 3-20 |

| 3–9  | SDRAM Configuration Register (SDRAM_CONFIG)                                                 | 3-30 |

| 3–10 | SDRAM Refresh Counter Register (SDRAM_REF_COUNT)                                            | 3-34 |

| 3–11 | SDRAM Control Register (SDRAM_CNTL)                                                         | 3-35 |

| 3–12 | SDRAM Initialization Refresh Counter Register (SDRAM_INIT_CONF)                             | 3-36 |

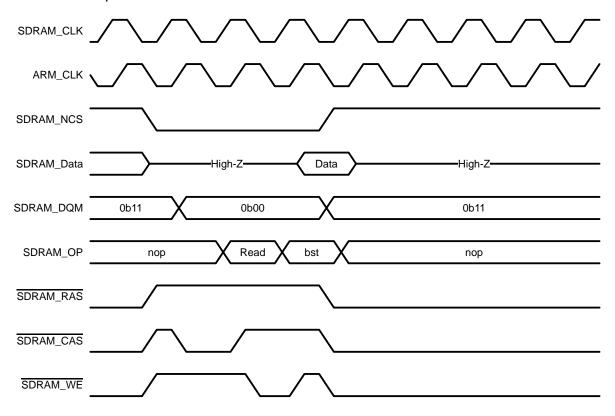

| 3–13 | Write Operation With Row Already Enabled – Parameters: tcas = 2, trc = 4, trp = 1           | 3-37 |

| 3–14 | Read Operation With Row Already Activated – Parameters: tcas = 2, trc = 4, trp = 1          |      |

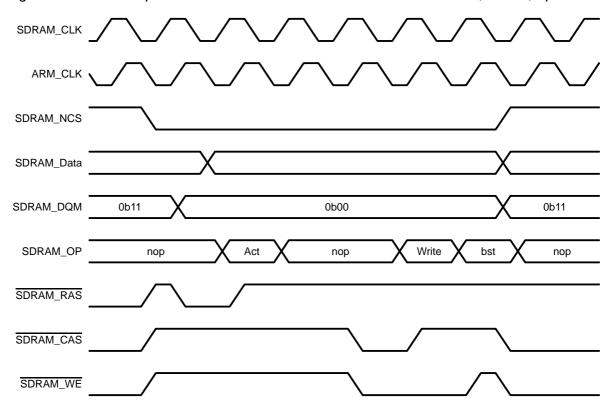

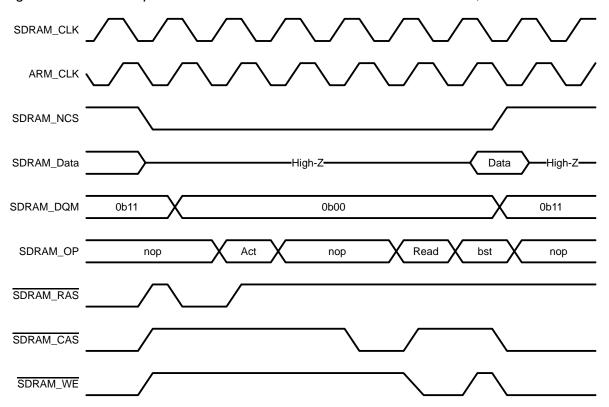

| 3–15 | Write Operation With Row Disabled – Parameters: tcas = 2, trc = 4, trp = 1                  |      |

| 3–16 | Read Operation With Row Disabled – Parameters: tcas = 2, trc = 4                            | 3-40 |

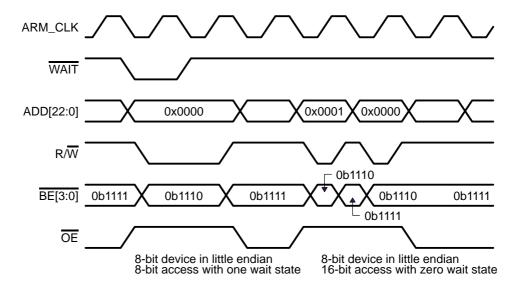

| 3–17 | 8-Bit Device Transaction in Little Endian                                                   | 3-41 |

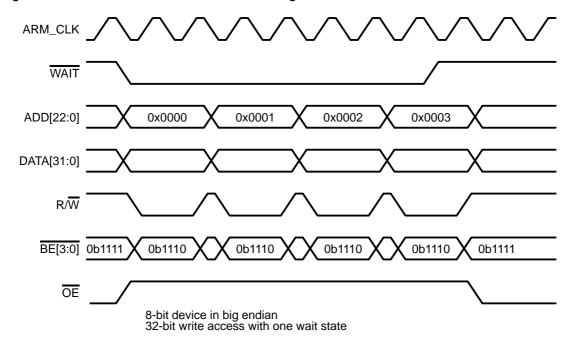

| 3–18 | 32-Bit Write Access on 8-Bit Big-Endian Device With One Wait State                          | 3-41 |

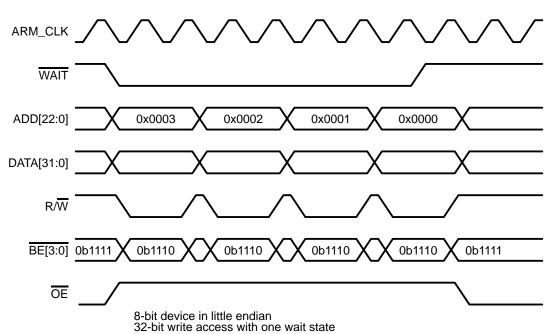

| 3–19 | 32-Bit Write Access on 8-Bit Little-Endian Device With One Wait State                       | 3-42 |

| 3-20 | 8-Bit Accesses on 32-Bit Device                                                             | 3-43 |

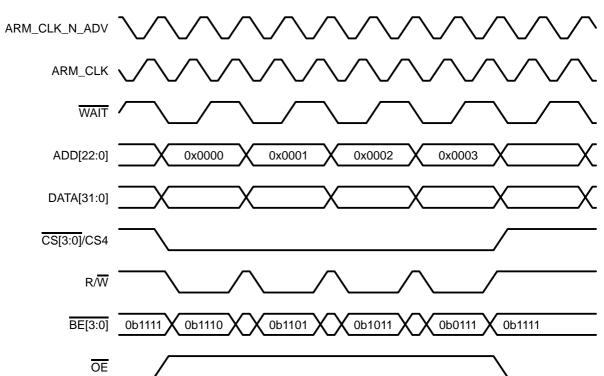

| 3–21 | 16-Bit accesses on 32-Bit Device                                                            | 3-44 |

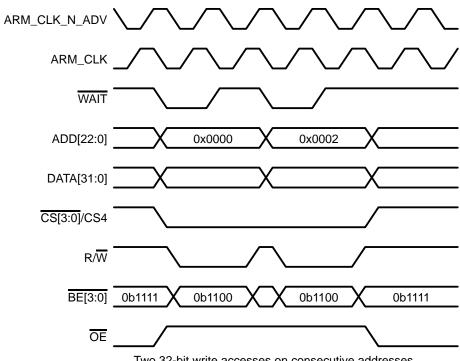

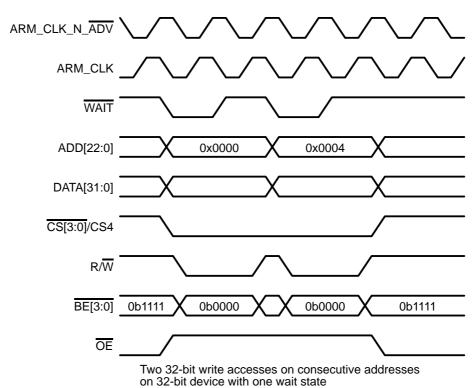

| 3–22 | 32-Bit Accesses on 32-Bit Device                                                            | 3-45 |

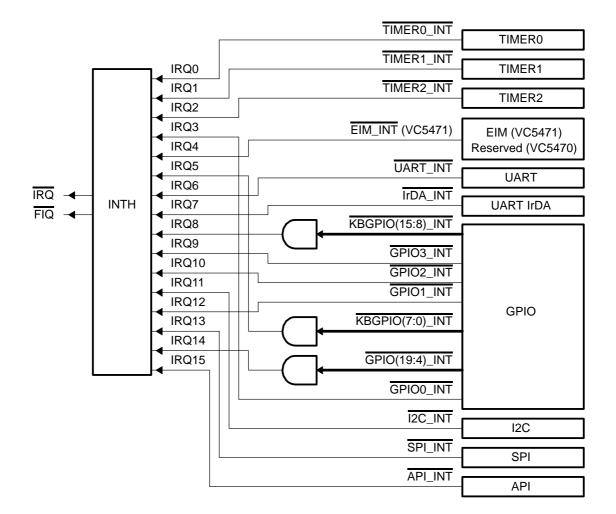

| 4–1  | ARM Peripheral Interrupt Mapping Diagram                                                    | 4-5  |

| 4–2  | Interrupt Register (IT_REG)                                                                 |      |

| 4–3  | Mask Interrupt Register (MASK_IT_REG)                                                       |      |

| 4–4  | Source IRQ Register (SRC_IRQ_REG)                                                           | 4-11 |

| 4–5  | Source FIQ Register (SRC_FIQ_REG)                                                           |      |

| 4–6  | Interrupt Control Register (INT_CTRL_REG)                                                   | 4-13 |

| 4–7  | IRQ Sleep Register (IRQ_SLEEP_REG)                      | 4-13 |

|------|---------------------------------------------------------|------|

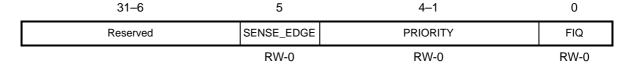

| 4–8  | Interrupt Level Register 0 (ILR_IRQ_0)                  | 4-15 |

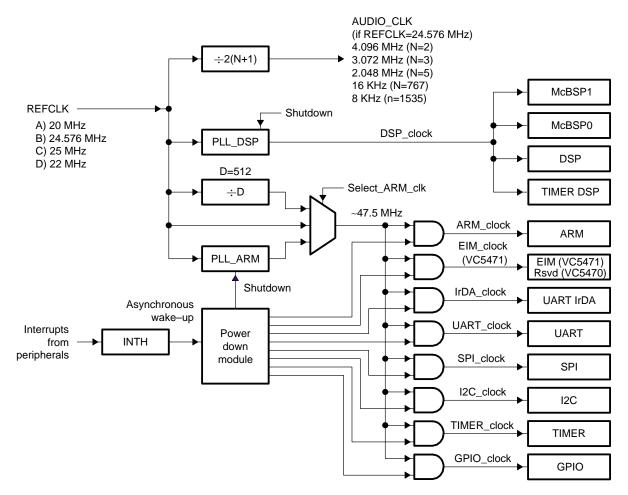

| 5–1  | Clock Management Module                                 | 5-4  |

| 5–2  | DSP Phase-Locked Loop Register (DSP_REG)                | 5-7  |

| 5–3  | Reset Control Register (CLKM_CNTL_RESET)                | 5-10 |

| 5–4  | Clock Configuration Register (CLKM_REG)                 |      |

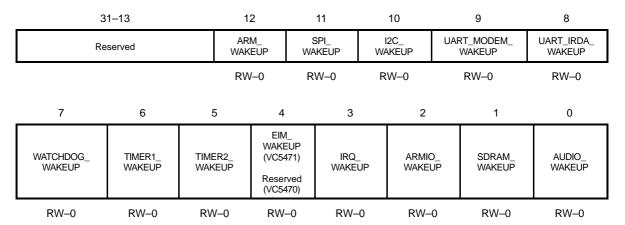

| 5–5  | Interrupt Clock Wakeup Register (WAKEUP_REG)            | 5-13 |

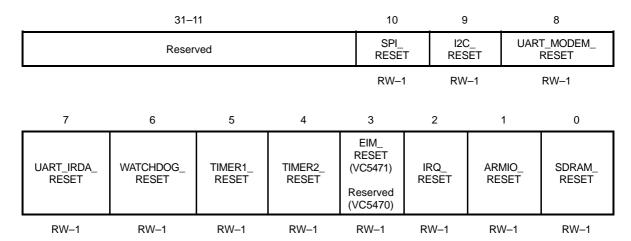

| 5–6  | Reset Register (RESET_REG)                              |      |

| 5–7  | Audio Rate Register (AUDIO_CLK)                         | 5-17 |

| 5–8  | Watchdog Status Register (WATCHDOG_STATUS)              | 5-18 |

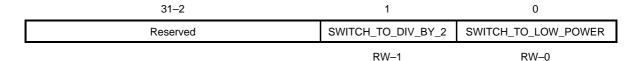

| 5–9  | Low-Power Mode Register (LOW_POWER_REG)                 | 5-19 |

| 5–10 | Low-Power Register Value Register (LOW_POWER_REG_VALUE) | 5-20 |

| 5–11 | PLL Clock Control Register (PLL_REG) – ARMSS            | 5-22 |

| 5–12 | CLKMD Clock Control Register (CLKMD) – DSPSS            | 5-25 |

| 6–1  | Timer0 Control Register (CNTL_TIMER0)                   | 6-5  |

| 6–2  | Timer0 Current Value Register (READ_TIM0)               | 6-6  |

| 6–3  | Timer1,2 Control Registers (CNTL_TIMER1,2)              | 6-8  |

| 6–4  | Timer1,2 Current Value Registers (READ_TIM1,2)          | 6-9  |

| 7–1  | GPIO_IO Register                                        | 7-5  |

| 7–2  | GPIO_CIO Register                                       | 7-6  |

| 7–3  | GPIO_IRQA Register                                      | 7-7  |

| 7–4  | GPIO_IRQB Register                                      | 7-8  |

| 7–5  | GPIO_DDIO – Delta Detect Register                       | 7-9  |

| 7–6  | GPIO_EN Register                                        | 7-10 |

| 7–7  | KBGPIO_IO Register                                      | 7-11 |

| 7–8  | KBGPIO_CIO Register                                     | 7-12 |

| 7–9  | KBGPIO_IRQA Register                                    | 7-13 |

| 7–10 | KBGPIO_IRQB Register                                    | 7-14 |