# TMS320C50/TMS320C51 Evaluation Module

# *Technical Reference*

*1998*

**DSP** Development Systems

TMS320C50/TMS320C51 Evaluation Module Technical Reference

> 503481-0001 Rev. C March 1998

SPECTRUM DIGITAL, INC. 10853 Rockley Road Houston, TX. 77099 Tel: 281/561-6952 Fax: 281/561-6037 sales@spectrumdigital.com www.spectrumdigital.com

#### **IMPORTANT NOTICE**

Spectrum Digital, Inc. reserves the right to make changes to its products or to discontinue any product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

Spectrum Digital, Inc. warrants performance of its products and related software to current specifications in accordance with Spectrum Digital's standard warranty. Testing and other quality control techniques are utilized to the extent deemed necessary to support this warranty.

Please be aware that the products described herein are not intended for use in life-support appliances, devices, or systems. Spectrum Digital does not warrant nor is liable for the product described herein to be used in other than a development environment.

Spectrum Digital, Inc. assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does Spectrum Digital warrant or represent any license, either express or implied, is granted under any patent right, copyright, or other intellectual property right of Spectrum Digital, Inc. covering or relating to any combination, machine, or process in which such Digital Signal Processing development products or services might be or are used.

#### WARNING

This equipment is intended for use in a laboratory test environment only. It generates, uses, and can radiate radio frequency energy and has not been tested for compliance with the limits of computing devices pursuant to subpart J of part 15 of FCC rules, which are designed to provide reasonable protection against radio frequency interference. Operation of this equipment in other environments may cause interference with radio communications, in which case the user at his own expense will be required to take whatever measures may be required to correct this interference.

#### TRADEMARKS

MS-DOS, MS-Windows, and Windows 95 are registered trademarks of Microsoft Corp.

Copyright © 1998 Spectrum Digital, Inc.

## Contents

| 1 | Introduction to the TMS320C5X Evaluation Module                                        | 1-1  |

|---|----------------------------------------------------------------------------------------|------|

|   | Provides you with a description of the TMS320C5X Evaluation Module, key features, and  |      |

|   | board outline.                                                                         |      |

|   | 1.0 Overview of the TMS320C5X EVM                                                      | 1-2  |

|   | 1.1 Key Features of the TMS320C5X EVM                                                  | 1-2  |

|   | 1.2 Functional Overview of the TMS320C5X EVM                                           | 1-3  |

| 2 | TMS320C5X EVM Operation                                                                | 2-1  |

|   | Describes the operation of the EVM320C5X. Information is provided on the EVM's various |      |

|   | interfaces.                                                                            |      |

|   | 2.0 The EVM320C5X Operation                                                            | 2-2  |

|   | 2.1 The EVM320C5X Board                                                                | 2-2  |

|   | 2.1.1 Power Connector, J1                                                              | 2-2  |

|   | 2.2 TMS320C5X Memory Interface                                                         | 2-3  |

|   | 2.2.1 Memory Mapping                                                                   | 2-8  |

|   | 2.3 Expansion Bus                                                                      | 2-10 |

|   | 2.3.1 Expansion I/O Connector, P1                                                      | 2-11 |

|   | 2.3.2 Expansion Analog Connector, P2                                                   | 2-12 |

|   | 2.3.3 Expansion Address and Data Connector, P3                                         | 2-13 |

|   | 2.3.4 Expansion Control Connector, P4                                                  | 2-14 |

|   | 2.4 Analog Interface                                                                   | 2-15 |

|   | 2.4.1 Analog Input, J2                                                                 | 2-15 |

|   | 2.4.2 Analog Output, J3                                                                | 2-15 |

|   | 2.5 JTAG Interface, P7                                                                 | 2-16 |

|   | 2.6 On Board Serial Interface, P5                                                      | 2-16 |

|   | 2.7 Jumpers                                                 | 2-18 |

|---|-------------------------------------------------------------|------|

|   | 2.7.1 J2 Coupling Select Jumper, JP1                        | 2-19 |

|   | 2.7.2 UART Reset Jumper, JP2                                | 2-19 |

|   | 2.7.3 Onboard UART CTS Routing Jumper, JP3                  | 2-19 |

|   | 2.7.4 Synchronous Serial Port Routing Jumper, JP4           | 2-20 |

|   | 2.7.5 AD55 Reset Jumper, JP5                                | 2-20 |

|   | 2.7.6 CLKIN Source Select Jumper, JP6, JP7, and JP10        | 2-20 |

|   | 2.7.7 Ready Routing Jumper, JP8                             | 2-21 |

|   | 2.7.8 Onboard UART Interrupt Select Jumper, JP9             | 2-21 |

|   | 2.7.9 C50 Bootloader Jumper, JP11                           | 2-21 |

|   | 2.7.10 Pseudo Boot Loader Enable Jumper, JP12               | 2-22 |

|   | 2.8 LEDs                                                    | 2-22 |

|   | 2.9 Resets                                                  | 2-22 |

| Α | TMS320C5X EVM PAL Equations                                 | A-1  |

|   | Lists the PAL equations that are used on the TMS320C5X EVM  |      |

|   | A.1 Memory Decode PAL Equations                             | A-2  |

|   | A.2 I/O Control PAL Equations                               | A-6  |

| В | TMS320C5X Schematics                                        | B-1  |

|   | Contains the schematics for the TMS320C5X EVM               |      |

| С | TL16C550 Data Sheet                                         | C-1  |

|   | Contains the technical information for the TL16C550         |      |

| D | TLC320AD55 Data Sheet                                       | D-1  |

|   | Contains the technical information for the TLC320AD55       |      |

| Е | EVM320 Mechanical Information                               | E-1  |

|   | Contains the mechanical information about the TMS320C5X EVM |      |

#### **About This Manual**

This document describes the board level operations of the TMS320C50/TMS320C51 evaluation module (EVM). The EVM is based on the Texas Instruments TMS320C50 and TMS320C51Digital Signal Processor.

The TMS320C5X EVM is a table top card to allow engineers and software developers to evaluate certain characteristics of the TMS320C50 and TMS320C51 DSP to determine if the processor meets the designers application requirements. Evaluators can create software to execute onboard or expand the system in a variety of ways.

#### **Notational Conventions**

This document uses the following conventions.

The TMS320C50 will sometimes be referred to as the C50 or C5X.

The TMS320C51 will sometimes be referred to as the C51 or C5X.

Program listings, program examples, and interactive displays are shown is a special italic typeface. Here is a sample program listing.

equations !rd = !strobe&rw;

#### **Information About Cautions**

This book may contain cautions.

This is an example of a caution statement.

A caution statement describes a situation that could potentially damage your software, or hardware, or other equipment. The information in a caution is provided for your protection. Please read each caution carefully.

#### **Related Documents**

Texas Instruments TMS320C5X Users Guide Texas Instruments TMS320 Fixed Point Assembly Language Users Guide Texas Instruments TMS320 Fixed Point C Language Users Guide Texas Instruments TMS320 Fixed Point C Source Debugger Users Guide Texas Instruments TLC320AD55C Data Manual - SLAS085 Texas Instruments TLC320AD55 Evaluation Board Application Report - SLAE11

## Chapter 1 Introduction to the TMS320C5X Evaluation Module

This chapter provides you with a description of the TMS32C5X Evaluation Module along with the key features and a block diagram of the circuit board.

| Topic |                                          | Page |

|-------|------------------------------------------|------|

| 1.0   | Overview of the TMS320C5X EVM            | 1-2  |

| 1.1   | Key Features of the TMS320C5X EVM        | 1-2  |

| 1.2   | Functional Overview of the TMS320C5X EVM | 1-3  |

#### 1.0 Overview of the TMS320C5X EVM

The TMS320C5X evaluation module(EVM) is a stand-alone card that lets evaluators examine certain characteristics of the TMS320C50 or TMS320C51 digital signal processor(DSP) to determine if this DSP meets their application requirements. Furthermore, the module is an excellent platform to develop and run software on the C5X family of processors.

The C5X EVM is shipped with a choice of DSPs; the TMS320C50, the TMS320C51, the TMS320BC51, or other pin compatible family members as they become available. The EVM allows full speed verification of C5X code. With at least 544 words of onchip memory, 128K words of onboard memory, onchip/onboard boot flash rom, on chip UART, on board UART, and a TLC320AD55 sigma delta codec the board can solve a variety of problems as shipped. Four expansion connectors are provided for any necessary evaluation circuitry not provided on the as shipped configuration.

To simplify code development and shorten debugging time a number of optional user interfaces are provided.

#### 1.1 Key Features of the TMS320C5X EVM

The C5X EVM has the following features:

- C50 operating at 40 Mips with 128K words of zero wait state memory C51/BC51 operating at 40 Mips

- TLC320AD55 Sigma Delta Codec with RCA Jack input and output

- On board UART with RS232 Drivers

- 32K words on board Flash ROM

- 4 Expansion Connectors

- On board IEEE 1149.1 JTAG Connection for Optional Emulation

- 5 Volt Only Operation

#### 1.2 Functional Overview of the TMS320C5X EVM

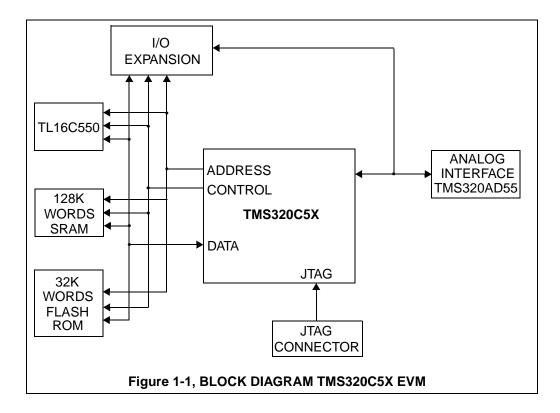

Figure 1-1 shows a block diagram of the basic configuration for the C5X EVM. The major interfaces of the EVM include the target ram and rom interface, target UART, analog interface, and expansion interface.

The C5X interfaces to 128K Words of zero wait-state static memory. An external I/O interface supports 65,000 parallel I/O ports and optional high speed synchronous serial port. A Flash Rom is mapped into the global memory interface. RCA jacks provide input and outputs to and from the AD55 sigma delta codec.

Spectrum Digital, Inc

## Chapter 2 Operation of the TMS320C5X Evaluation Module

This chapter describes the operation of the TMS32C5X Evaluation Module along with the key interfaces and an outline of the circuit board.

| Topic  |                                             | Page |

|--------|---------------------------------------------|------|

| 2.0    | The EVM320C5X Operation                     | 2-2  |

| 2.1    | The EVM320C5X Board                         | 2-2  |

| 2.1.1  | Power Connector, J1                         | 2-2  |

| 2.2    | TMS320C5X Memory Interface                  | 2-3  |

| 2.2.1  | Memory Mapping                              | 2-8  |

| 2.3    | Expansion Bus                               | 2-10 |

| 2.3.1  | Expansion I/O Connector, P1                 | 2-11 |

| 2.3.2  | Expansion Analog Connector, P2              | 2-12 |

| 2.3.3  | Expansion Address and Data Connector, P3    | 2-13 |

| 2.3.4  | Expansion Control Connector, P4             | 2-14 |

| 2.4    | Analog Interface                            | 2-15 |

| 2.4.1  | Analog Input, J2                            | 2-15 |

| 2.4.2  | Analog Output, J3                           | 2-15 |

| 2.5    | JTAG Interface, P7                          | 2-16 |

| 2.6    | On Board Serial Interface, P5               | 2-16 |

| 2.7    | EVM320C5X Jumpers                           | 2-18 |

| 2.7.1  | J2 Input Coupling Select Jumper, J1         | 2-19 |

| 2.7.2  | UART Reset Jumper, JP2                      | 2-19 |

| 2.7.3  | Onboard UART CTS Routing Jumper, J3         | 2-19 |

| 2.7.4  | Synchronous Serial Port Routing Jumper, JP4 | 2-20 |

| 2.7.5  | AD55 Reset Jumper, JP5                      | 2-20 |

| 2.7.6  | CLKIN Source Select Jumper, JP6, JP7, JP10  | 2-20 |

| 2.7.7  | Ready Routing Jumper, JP8                   | 2-21 |

| 2.7.8  | Onboard UART Interrupt Select Jumper, JP9   | 2-21 |

| 2.7.9  | C50 Bootloader Jumper, JP11                 | 2-21 |

| 2.7.10 | Pseudo Boot Loader Enable Jumper, JP12      | 2-22 |

| 2.8    | LEDS                                        | 2-22 |

| 2.9    | Resets                                      | 2-22 |

#### 2.0 The EVM320C5X Operation

This chapter describes the C5X Evaluation module, its key components, and how they operate. It also provides information on the EVM's various interfaces. The C5X EVM consists of five major blocks of logic.

- C5X memory interface

- Analog Interface

- On board serial interface

- Expansion connector interface

- JTAG interface

#### 2.1 The TMS320C5X EVM Board

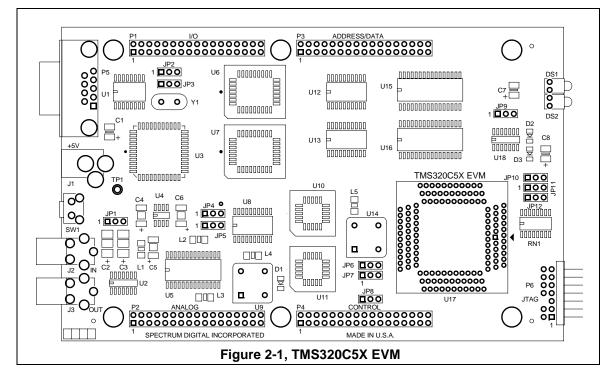

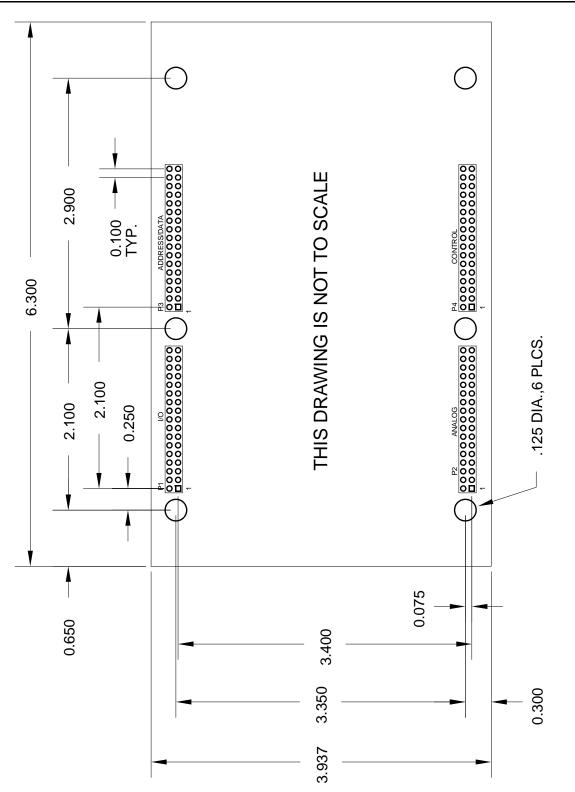

The EVM320C5X is a 3U sized board which is powered by an external 5 Volt only power supply. Figure 2-1 shows the layout of the C5X EVM.

#### 2.1.1 Power Connector, J1

The C5X is powered by a 5 Volt only power supply which is available with the module. The board requires 750 milliamps. The power is supplied via 2 millimeter jack J1. If expansion boards are connected to the module a higher amperage power supply may be necessary.

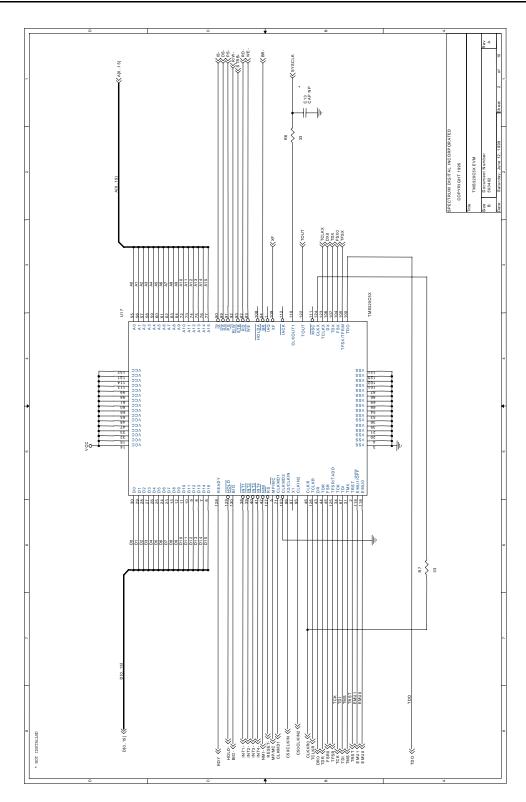

#### 2.2 TMS320C5X Memory Interface

The EVM includes 64k words of zero wait-state program ram memory and 64k words of zero wait-state data ram memory, providing a total of 128 k words of off chip static ram. The board also features 2 external 32K byte flash roms. These roms are located in the global memory space and can be used to boot load programs with the onchip boot loader or can be mapped in program space and copied into ram and disabled with the pseudo boot loader. A jumper (JP11) is connected to the MC/MP pin and allows users to enable or disable the on chip bootloader at power up (C50, BC51 only)

Figure 2-2 and 2-3 show the EVM's memory map. It is important to remember that internal memory has a higher precedence than the external memory. For more information on the memory in the device populated in your EVM card please refer to Texas Instruments TMS320C5X Users Guide. Futhermore, it is important to take into account that external memory is affected by wait-states. Wait state generation is done with the PDWSR, CWSR, and IOWSR on chip wait-state generation registers and off chip with the ready signal. To obtain zero waitstate memory in both the program and data memory spaces the on-chip wait-state generators must be appropriately programmed. The board powers up with 7 wait-states. The EVM board does not generate wait states via the ready signal for external program and data memory accesses. Only external I/O accesses to on-board peripherals generate a not ready signal. The I/O Wait States should not be set to less than 3 in the IOSWR Register.

|                                      | ogram Spac                          | ce                                             | Data Space                                             | l                          | Data Space                                       |

|--------------------------------------|-------------------------------------|------------------------------------------------|--------------------------------------------------------|----------------------------|--------------------------------------------------|

| 0x0000<br>0x1FFF_<br>0x2000          | External<br>RAM                     | 0x0000<br>0x005F                               | Memory<br>Mapped<br>Registers                          | 0x0000<br>0x005F           | Memory<br>Mapped<br>Registers                    |

| 0x2000                               | On Chip<br>SARAM<br>RAM = 1         | 0x005F<br>0x0060<br>0x007F                     | On Chip<br>B2 RAM                                      | 0x005F<br>0x0060<br>0x007F | On Chip<br>B2 RAM                                |

|                                      | RAM = 0<br>External<br>RAM          | 0x0080<br>0x00FF                               | Reserved                                               | 0x0080<br>0x00FF           | Reserved                                         |

| 0x2BFF<br>0x3000<br>0xFDFF<br>0xFE00 | External<br>RAM                     | 0x0100                                         | On Chip<br>B0 RAM<br>if CNF=0,<br>Reserved<br>if CNF=1 | 0x0100                     | On Chip<br>B0 RAM<br>if CNF=0,<br>Reserved       |

|                                      | B0 RAM<br>CNF = 1<br>External 0x030 | 0x02FF<br>0x0300<br>0x04FF<br>0x0500<br>0x07FF | On Chip<br>RAM                                         | 0x02FF<br>0x0300<br>0x04FF | if CNF=1<br>On Chip<br>RAM                       |

| 0xFFFF                               | RAM<br>CNF = 0                      |                                                | 0x07FF                                                 | Reserved                   | 0x0500<br>0x07FF                                 |

| L                                    |                                     | 0x0800<br>0x2BFF                               | On Chip<br>SARAM<br>OVLY=1<br>External<br>OVLY=0       | 0x0800<br>0x2BFF           | On Chip<br>SARAM<br>OVLY=1<br>External<br>OVLY=0 |

|                                      |                                     | 0x2C00<br>0x7FFF                               | External<br>RAM                                        | 0x2C00<br>0x7FFF           | External<br>RAM                                  |

|                                      |                                     | 0x8000<br>0xFFFF                               | External<br>RAM                                        | 0x8000<br>0xFFFF           | Flash<br>ROM<br>Global<br>Space                  |

|                                      | Figur                               | e 2-2, C5                                      | BR=0<br>OUT3 = 0<br>50 EVM Mem                         | nory Map                   | BR=1<br>OUT3 = 0                                 |

The memory map for the EVM with a C50 DSP is shown below:

|                  | rogram Spa                                      |                  | rogram Spac                              | ce                                             | Data Space                                       | [                                              | Data Space                                       |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------|------------------|------------------------------------------|------------------------------------------------|--------------------------------------------------|------------------------------------------------|--------------------------------------------------|--|--|--|--|--|--|--|

| 0x0000<br>0x1FFF | External<br>RAM                                 | 0x0000           | External<br>Flash ROm<br>with            | 0x0000                                         | Memory<br>Mapped<br>Registers                    | 0x0000                                         | Memory<br>Mapped<br>Registers                    |  |  |  |  |  |  |  |

| 0x2000           | On Chip<br>SARAM<br>RAM = 1                     |                  | shadowed<br>writes to<br>RAM<br>OUT3 = 0 | 0x005F<br>0x0060<br>0x007F                     | On Chip<br>B2 RAM                                | 0x005F<br>0x0060<br>0x007F                     | On Chip<br>B2 RAM                                |  |  |  |  |  |  |  |

| 0x23FF           | RAM = 0<br>External<br>RAM                      |                  | External<br>or<br>RAM                    | 0x0080<br>0x00FF                               | Reserved                                         | 0x0080<br>0x00FF                               | Reserved                                         |  |  |  |  |  |  |  |

| 0x2400<br>0xFDFF | External<br>RAM                                 | 0x7FFF<br>0x8000 | OUT3 = 1<br>External                     | 0x0100                                         | On Chip<br>B0 RAM<br>if CNF=0,<br>Reserved       | 0x0100                                         | On Chip<br>B0 RAM<br>if CNF=0,<br>Reserved       |  |  |  |  |  |  |  |

| 0xFE00           | On Cnip<br>B0 RAM<br>CNF = 1<br>External<br>RAM | 0xFFFF           | RAM                                      | 0x02FF<br>0x0300<br>0x04FF<br>0x0500<br>0x07FF | if CNF=1<br>On Chip<br>RAM                       | 0x02FF<br>0x0300<br>0x04FF<br>0x0500<br>0x07FF | if CNF=1<br>On Chip<br>RAM                       |  |  |  |  |  |  |  |

| 0xFFFF           |                                                 |                  | Pseudo<br>Loader<br>Disabled             |                                                | Reserved                                         |                                                | Reserved                                         |  |  |  |  |  |  |  |

|                  |                                                 | 1                | Disableu                                 | 0x0800<br>0x0BFF                               | On Chip<br>SARAM<br>OVLY=1<br>External<br>OVLY=0 | 0x0800<br>0x0BFF                               | On Chip<br>SARAM<br>OVLY=1<br>External<br>OVLY=0 |  |  |  |  |  |  |  |

|                  |                                                 | 0x7              | 0x0C00<br>0x7FFF                         | External<br>RAM                                | 0x0C00<br>0x7FFF                                 | External<br>RAM                                |                                                  |  |  |  |  |  |  |  |

|                  |                                                 |                  |                                          | 0x8000<br>0xFFFF                               | External<br>RAM                                  | 0x8000<br>0xFFFF                               | Flash<br>ROM<br>Global<br>Space                  |  |  |  |  |  |  |  |

|                  |                                                 |                  |                                          | -                                              | BR=0<br>OUT3 = 0                                 | _                                              | BR=1<br>OUT3 = 0                                 |  |  |  |  |  |  |  |

|                  |                                                 | Figu             | ure 2-3, C51                             | EVM Me                                         | emory Map                                        | Figure 2-3, C51 EVM Memory Map                 |                                                  |  |  |  |  |  |  |  |

The memory map for the EVM with a C51 DSP is shown below:

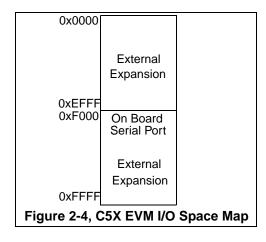

The I/O space map for the EVM is shown below:

The C5X EVM can be configured in a variety of ways. The following is a brief outline of configuration for both the C50 and C51.

The standard as shipped configuration, for the C50 and C51 is an all RAM system which is controlled via jumper JP12. When JP12 is in the 1-2 position and JP11 (which controls the MP/MC- pin) is in the 1-2 position the entire data space and program space are RAM based. Flash ROM is mapped in global data space from 0x8000 to 0xFFFF, but can be deactivated by writing a 1 to the OUT3 bit in the UART's MCR register.

When the user desires to use the EVM in a stand-alone mode either the C50 bootloader or the EVM's pseudo boot loader must be used to allow applications stored in flash to be copied into RAM and executed.

To use the pseudo boot loader jumper JP12 is placed in the 2-3 position with the JP11 jumper in the 1-2 position. In this mode the flash rom is readable in program space 0x0000 to 0x7FFF and read-writable in global data space 0x8000 to 0xFFFF. Writes to 0x0000 to 0x7FFF in program space access external RAM thus the flash rom is "shadowed" by ram allowing the user application to copy itself to ram and begin execution. The primary reason to copy the program to ram is to allow DSP to operate at 0 wait states. After the code is copied into RAM the OUT3 bit is set to 1 disabling the FLASH ROM.

If EVM is populated with a C50 or BC51device the user can use either the pseudo boot loader as previously discussed or the C50's internal boot loader. The EVM supports parallel prom boot mode via the C50's internal boot loader. In this configuration JP11 is in the2-3 position enabling the boot loader, and JP12 is in the 1-2 position enabling the flash rom in global address space. The C50 boot loader will access location 0xFFFF in global data space to identify a key for boot loading. The keys that are applicable for the EVM is shown in the table below.

| Address | D15       | D8 | D7       | D0 | Mode                  |

|---------|-----------|----|----------|----|-----------------------|

| 0xFFFF  | XXXX XXXX |    | SRC   01 |    | 8 bit parallel EPROM  |

| 0xFFFF  | XXXX XXXX |    | SRC      | 10 | 16 bit parallel EPROM |

Table 1: Boot Load Keys

The SRC address is the 6 Most Significant Bits (MSBs) of the flash ROM's start address where the boot loadable data is located. In the case of the C5X this typically would be location 0x8000 so the SRC would be 100000b.

The data stored at the SRC field needs to be in one of the following formats shown in Table 2 and Table 3.

| Address | Field Definition    |

|---------|---------------------|

| 0x8000  | Destination Address |

| 0x8001  | Length              |

| 0x8002  | Code word #1        |

|         | etc.                |

| Table 2: 16 Bit S | <b>SRC Field</b> | Definitions |

|-------------------|------------------|-------------|

|-------------------|------------------|-------------|

Destination is the destination address of where the code will be written, typically 0x0000. Length is the number of 16 bit words to be transferred -1, not including the 2 header words. After the C50 has transferred the data, execution is started at the destination address.

#### Spectrum Digital, Inc

The 8 bit boot mode is similar except that only the lower 8 bits are used and the first location is the MSB. This is shown in the table below:

| Address | Field Definition<br>D7 D0      |

|---------|--------------------------------|

| 0x8000  | Destination Address, high byte |

| 0x8001  | Destination Address, low byte  |

| 0x8002  | Length, high byte              |

| 0x8003  | Length, low byte               |

| 0x8004  | Code word 1, high byte         |

| 0x8005  | Code word 1, low byte          |

Table 3: 8 Bit SRC Field Definitions

#### 2.2.1 Memory Mapping

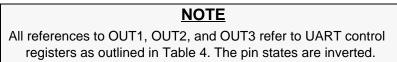

Memory mapping is controlled by the jumper JP12 and software output pin OUT3 from the TL16C550 UART as described in the previous section. The table below summarizes the mapping.

Table 4: Memory Map Control Bits

| JP12 | OUT3(DTR) | Description                                                                                    |

|------|-----------|------------------------------------------------------------------------------------------------|

| 1-2  | 0         | Flash Mapped in Global Data Space 0x8000-0xFFFF                                                |

| 1-2  | 1         | Flash Disabled                                                                                 |

| 2-3  | 0         | Flash Mapped in Global Data Space 0x8000-0xFFFF<br>and shadowed in Program Space 0x0000-0x7FFF |

| 2-3  | 1         | Flash Disabled                                                                                 |

CLKOUT ADDRESS DATA READ WRITE RW PS\* DS\* STR\* RAMOE\* RAMOE\* RAMWE\* Figure 2-5, Zero Wait State Memory Timing

External memory decode is done via U10 a GAL16V8. The generic array device selects the RAM, FLASH ROM, on board peripherals, or off board peripherals. The equations for the GAL are included in Appendix A. Figure 2-4 shows a zero wait state program space memory read followed by a data space memory write.

The external Flash ROM is mapped into the global data space or program space. Note that this memory requires multiple wait states. The main purpose of this memory is to allow for the boot loading of programs from either the C5X's internal boot loader or the pseudo boot loader created in external flash. For more information on the boot loader please refer to the Texas Instruments TMS320C5X Users Guide.

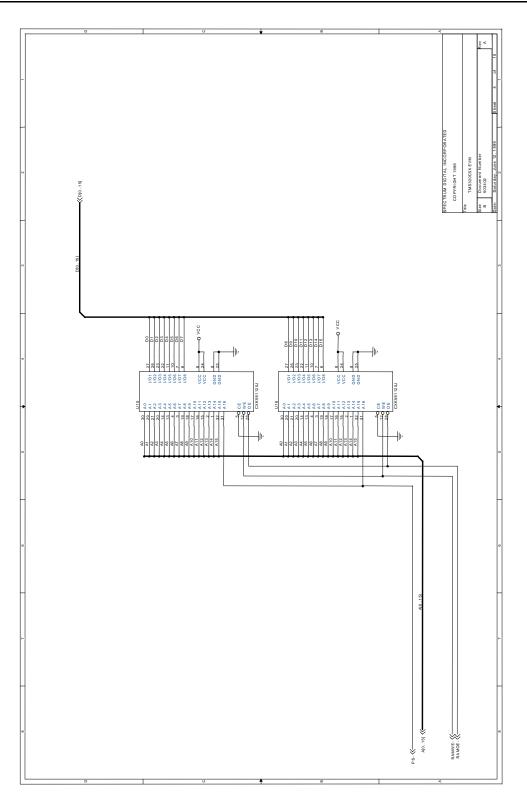

#### 2.3 Expansion Bus

The TMS320C5X EVM has 4 expansion connectors. Each of these carry a specific type of signals. These connectors are used for hardware expansion or customization to meet the application's unique requirements. The four connectors are:

| Connector | Function     |

|-----------|--------------|

| P1        | I/O          |

| P2        | Analog       |

| P3        | Address/Data |

| P4        | Control      |

#### Table 5: Expansion Connectors

I/O accesses from 0x0000 to 0xEFFF are mapped onto the I/O connector. The address data and control lines are not buffered onto these busses. The expansion I/O busses are meant to execute with at least 3 wait states in the IOWSR register to accommodate the onboard UART. However the ready signal can be asserted if a longer access time is required. The next 4 tables describe these connectors.

#### 2.3.1 Expansion I/O Connector, P1

The definition of P1, which has the I/O signals is shown below.

| Pin # | Signal        | Pin # | Signal        |  |

|-------|---------------|-------|---------------|--|

| 1     | VCC, +5 Volts | 2     | VCC, +5 Volts |  |

| 3     | TOUT          | 4     | Reserved      |  |

| 5     | TDR           | 6     | Reserved      |  |

| 7     | TDX           | 8     | Reserved      |  |

| 9     | TFSR          | 10    | Reserved      |  |

| 11    | TCLKR         | 12    | Reserved      |  |

| 13    | TCLKX         | 14    | OUT2          |  |

| 15    | 3             | 16    | Reserved      |  |

| 17    | GND           | 18    | GND           |  |

| 19    | XF            | 20    | BIO           |  |

| 21    | Resreved      | 22    | Reserved      |  |

| 23    | OUT1(UART)    | 24    | OUT3(UART)    |  |

| 25    | OUT2(UART)    | 26    | Reserved      |  |

| 27    | Reserved      | 28    | Reserved      |  |

| 29    | IN1(UART)     | 30    | IN3(UART)     |  |

| 31    | IN2(UART)     | 32    | Reserved      |  |

| 33    | GND           | 34    | GND           |  |

Table 6: P1 I/O

#### 2.3.2 Expansion Analog Connector, P2

The definition of P2, which has the analog signals is shown below.

| Pin # | Signal           | Pin # | Signal           |

|-------|------------------|-------|------------------|

| 1     | VCCA, +5V Analog | 2     | VCCA, +5V Analog |

| 3     | ADCIN 0 (AD55)   | 4     | Reserved         |

| 5     | Reserved         | 6     | Reserved         |

| 7     | Reserved         | 8     | Reserved         |

| 9     | Reserved         | 10    | Reserved         |

| 11    | FLAG 0 (AD55)    | 12    | FLAG 1 (AD55)    |

| 13    | Reserved         | 14    | Reserved         |

| 15    | Reserved         | 16    | Reserved         |

| 17    | Reserved         | 18    | Reserved         |

| 19    | Reserved         | 20    | Reserved         |

| 21    | Reserved         | 22    | -5V              |

| 23    | AGND             | 24    | AGND             |

| 25    | DACOUT 0 (AD55)  | 26    | Reserved         |

| 27    | Reserved         | 28    | Reserved         |

| 29    | Reserved         | 30    | Reserved         |

| 31    | Reserved         | 32    | Reserved         |

| 33    | AGND             | 34    | AGND             |

Table 7: P2 Analog

#### 2.3.3 Expansion Address and Data Connector, P3

The definition of P3, which has the address and data signals is shown below.

| Pin # | Signal | Pin # | Signal |

|-------|--------|-------|--------|

| 1     | A0     | 2     | A1     |

| 3     | A2     | 4     | A3     |

| 5     | A4     | 6     | A5     |

| 7     | A6     | 8     | A7     |

| 9     | A8     | 10    | A9     |

| 11    | A10    | 12    | A11    |

| 13    | A12    | 14    | A13    |

| 15    | A14    | 16    | A15    |

| 17    | GND    | 18    | GND    |

| 19    | D0     | 20    | D1     |

| 21    | D2     | 22    | D3     |

| 23    | D4     | 24    | D5     |

| 25    | D6     | 26    | D7     |

| 27    | D8     | 28    | D9     |

| 29    | D10    | 30    | D11    |

| 31    | D12    | 32    | D13    |

| 33    | D14    | 34    | D15    |

Table 8: P3 Address/Data

#### 2.3.4 Expansion Control Connector, P4

The definition of P4, which has the control signals is shown below.

| Pin # | Signal        | Pin # | Signal        |

|-------|---------------|-------|---------------|

| 1     | VCC, +5 Volts | 2     | VCC, +5 Volts |

| 3     | PS-           | 4     | DS-           |

| 5     | IS-           | 6     | BR-           |

| 7     | WE-           | 8     | RD-           |

| 9     | STRB-         | 10    | R/W           |

| 11    | READY         | 12    | Reserved      |

| 13    | RS-           | 14    | TRGRESET-     |

| 15    | NMI-          | 16    | INT2-         |

| 17    | GND           | 18    | GND           |

| 19    | INT3-         | 20    | INT4-         |

| 21    | DR            | 22    | Reserved      |

| 23    | DX            | 24    | Reserved      |

| 25    | FSR           | 26    | Reserved      |

| 27    | FSX           | 28    | Reserved      |

| 29    | CLKXR         | 30    | Reserved      |

| 31    | Reserved      | 32    | CLKOUT        |

| 33    | GND           | 34    | GND           |

Table 9: P4 Control

#### 2.4 Analog Interface

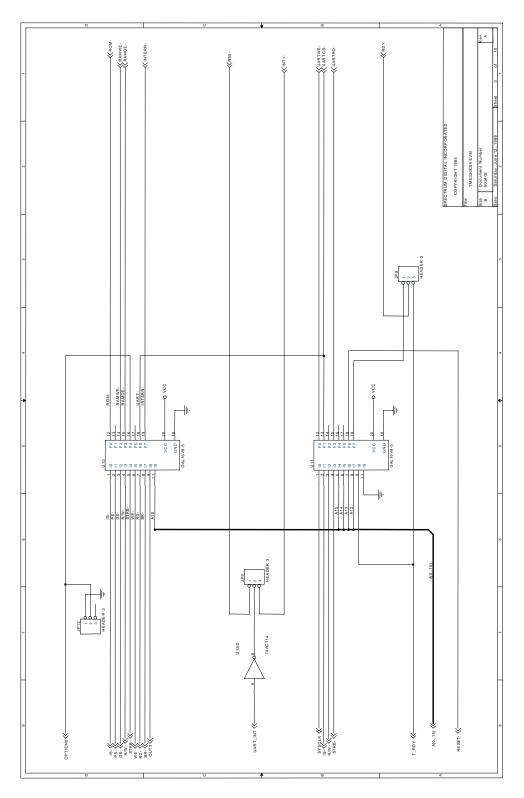

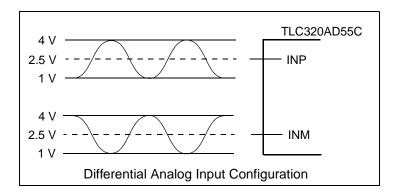

The C5X synchronous serial port can be used to access either the onboard TLC320AD55 sigma delta codec or be jumpered to the expansion connector. Jumper JP4 (1-2) is used to interconnect the serial port to the AD55. If the serial port is to be used from the expansion connector the plug should be in the 2-3 position.

| JP4 Position | Signal Source          |

|--------------|------------------------|

| 1-2          | TLC320AD55             |

| 2-3          | Expansion Connector P4 |

Programming information for the TLC320AD55 is contained in appendix D.

#### 2.4.1 Analog Input, J2

The analog input is driven from either RCA Jack J2 or expansion connector P2. The analog input can be either AC or DC coupled. Jumper JP1 determines if the input is AC or DC coupled.

#### Table 11: J2 Coupling

| JP1 Position | Input Coupling |

|--------------|----------------|

| 1-2          | DC Coupled     |

| 2-3          | AC Coupled     |

#### 2.4.2 Analog Output, J3

The analog output is driven to RCA Jack J3 and expansion connector P2.

#### 2.5 JTAG Interface, P7

The TMS320C5X Evaluation Module is supplied with a 14 pin header interface. This interface is labeled P7 and is the standard interface used by JTAG emulators to interface to Texas Instruments DSPs. The pinout for the connector is shown in the figure below:

| TMS      | 1                                 | 2  | TRST-        |                                     |  |

|----------|-----------------------------------|----|--------------|-------------------------------------|--|

| TDI      | 3                                 | 4  | GND          | Header Dimensions                   |  |

| PD (+5V) | 5                                 | 6  | no pin (key) | Pin-to-Pin spacing, 0.100 in. (X,Y) |  |

| TDO      | 7                                 | 8  | GND          | Pin width, 0.025-in. square post    |  |

| TCK-RET  | 9                                 | 10 | GND          | Pin length, 0.235-in. nominal       |  |

| ТСК      | 11                                | 12 | GND          |                                     |  |

| EMU0     | 13                                | 14 | EMU1         |                                     |  |

|          | Figure 2-6, JTAG Interface Pinout |    |              |                                     |  |

#### 2.6 On Board Serial Interface

The EVM320C5X has a TL16C550 UART (U3) which provides a serial interface. This UART is mapped into I/O space at locations 0xF000 to 0xF008. This device allows users to use this resource for data logging, code debugging and other applications.

The programming of the TL16C550 UART is described in appendix C.

This UART is brought out to connector P5 on the EVM320C5X. Connector P5 is a DB9 female connector. The pin positions for the P5 connector as viewed from the edge of the EVM320C5X.

Figure 2-7, P5 Connector

The pin numbers and their corresponding signals are shown in the table below:

| Pin # | PC (female) | SD EVM            |

|-------|-------------|-------------------|

| 2     | Rx, input   | Tx, output        |

| 3     | Tx, output  | Rx, input         |

| 4     | DTR, output | Reset/CTS, input* |

| 5     | GND         | GND               |

| 8     | CTS, input  | RTS, output       |

Table 12: P5 RS232 Pinout

\* Jumper JP3 can also be used to configure pin 4 to pin 7 on P5. This allows for normal handshaking. The jumper setting are shown in to table below:

Table 13: JP3 Settings

| JP3 Position | CTS Routing                |

|--------------|----------------------------|

| 1-2          | P5 pin 4 used on CTS input |

| 2-3          | P5 pin 7 used on CTS input |

Connector P5 pin 4 can be jumpered via JP9 to generate different interrupt levels. The type of interrupt is shown in the table below:

Table 14: Onboard UART Interrupt Selection

| JP9 Position | Interrupt Level |

|--------------|-----------------|

| 1-2          | NMI             |

| 2-3          | INT1            |

#### 2.7 EVM320C5X Jumpers

The EVM320C5X has 12 jumpers which determine how features on the EVM are utilized. The table below lists the jumpers and their function. The following sections describe the use of each jumper.

| Jumper # | Size  | Function                      |

|----------|-------|-------------------------------|

| JP1      | 1 x 3 | J2 Input Coupling             |

| JP2      | 1 x 3 | UART Reset/CTS                |

| JP3      | 1 x 3 | P5 pin 4 Routing              |

| JP4      | 1 x 3 | Synchronous Port Routing      |

| JP5      | 1 x 3 | AD55 Reset Option             |

| JP6      | 1 x 3 | CLKIN Source Select           |

| JP7      | 1 x 3 | CLKIN Source Select           |

| JP8      | 1 x 3 | Ready Option                  |

| JP9      | 1 x 3 | Onboard UART Interrupt Select |

| JP10     | 1 x 3 | CLKIN Source Select           |

| JP11     | 1 x 3 | C50 Bootloader Enable         |

| JP12     | 1 x 3 | Pseudo Boot Loader Enable     |

Table 15: EVM320C5X Jumpers

Each jumper on the EVM320C5X is a 1 x 3 jumper. Each 1 x 3 jumper **must** have the selection 1-2 or 2-3. The #2 pin is the center pin. The #1 pin has a square solder pad and can be seen from the solder side of the printed circuit board. This pin is usually marked with a '1' on the board's silkscreen. A top view of this type of jumper is shown below:

|                           |   | ٠ | • |  |

|---------------------------|---|---|---|--|

|                           | 1 | 2 | 3 |  |

| Figure 2-8, Jumper Layout |   |   |   |  |

WARNING ! Unless noted otherwise all jumpers must be installed in either the 1-2 or 2-3 position

#### 2.7.1 J2 Input Coupling Select Jumper, JP1

Jumper JP1 is used to select the coupling for the analog input. If position 1-2 is selected the coupling is DC. The 2-3 selection will provide AC coupling.

| JP1 Position | Input Coupling |

|--------------|----------------|

| 1-2          | DC Coupled     |

| 2-3          | AC Coupled     |

| Table | 16: | J2 | Coup | ling |

|-------|-----|----|------|------|

|-------|-----|----|------|------|

#### 2.7.2 UART Reset Jumper, JP2

Jumper JP2 is used to select either a system reset from the P5, pin 4 DTR line or to connect the DTR line to the UART's CTS pin. When position 1-2 is selected the DTR activates the reset. The 2-3 position connects DTR to CTS. The table below shows the positions and their functions:

#### Table 17: UART Reset

| JP2 Position | Function             |

|--------------|----------------------|

| 1-2          | DTR activates Reset  |

| 2-3          | Connects DTR to CTS* |

\* See jumper JP15 for choice of pin 4 or pin 7 to CTS on the onboard UART.

#### 2.7.3 On Board UART CTS Routing Jumper, JP3

Jumper JP3 is used to configure the source of the CTS signal on the onboard UART. When position 1-2 is used the pin 4 on P5 is used as the CTS input. If position 2-3 is chosen pin 7 on P5 is used as the CTS input.

#### Table 18: Onboard UART CTS Routing

| JP3 Position | CTS Routing                |

|--------------|----------------------------|

| 1-2          | P5 pin 4 used on CTS input |

| 2-3          | P5 pin 7 used on CTS input |

#### 2.7.4 Synchronous Serial Port Routing Jumper, JP4

The JP4 jumper is used to select the source of data for the synchronous serial port on the C5X. By selecting position 1-2 the synchronous serial port is connected to TLC320AD55 AIC. Position 2-3 connects the serial port to the expansion connector P4.

Table 19: Synchronous Serial Port Routing

| JP4 Position | Signal Source          |

|--------------|------------------------|

| 1-2          | TLC320AD55             |

| 2-3          | Expansion Connector P4 |

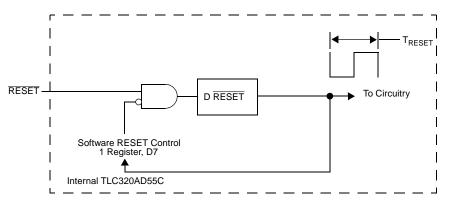

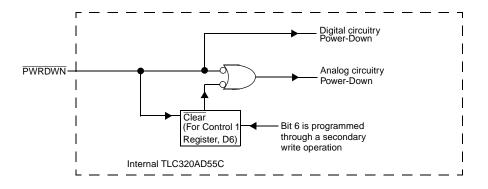

#### 2.7.5 AD55 Reset Jumper, JP5

The AD55 Codec can be reset either by the system reset or the I/O0 pin on the C5X. Position 1-2 allow the AD55 to be reset by the system reset. In position 2-3 the AD55 is reset from the I/O0 pin on the DSP. The table below shows the positions and their functions:

#### Table 20: AD55 Reset

| JP5 Position | Function                          |

|--------------|-----------------------------------|

| 1-2          | System reset activates AD55 reset |

| 2-3          | C5X I/O0 pin activates AD55 reset |

#### 2.7.6 CLKIN Source Select Jumper, JP6, JP7, JP10

The C5X EVM is equipped with a 40 Megahertz oscillator. Jumpers JP6, JP7, and JP10 determine if the output clkout frequency is 20 Megahertz (divide by 2, 20 MIPS) or 40 Megahertz (divide by 1, 40 MIPS). Note there are only two valid configurations.

| Table 21: | CLKIN | Source | Select |

|-----------|-------|--------|--------|

|-----------|-------|--------|--------|

| JP6 Position | JP7 Position | JP10 Position | Output Clock  |

|--------------|--------------|---------------|---------------|

| CLKIN        | CLKIN2       | CLKMDI        | C5X Pin       |

| 1-2          | 1-2          | 1-2           | 40 Mhz CLKOUT |

| 2-3          | 2-3          | 2-3           | 20 Mhz CLKOUT |

#### 2.7.7 READY Routing Jumper, JP8

READY to the C5X device from the GAL U11 can be deactivated if necessary. Of course this prevents use of the onboard UART if the wait state generator is set to less than 7 wait states. In normal mode (position 1-2) external READY from the I/O connector is routed through GAL U11. When JP8 is in the 2-3 position the READY signal is routed directly from the expansion connector to the C5X device. The table below shows the positions and their functions:

#### **Table 22: READY Routing**

| JP8 Position | Function                                    |

|--------------|---------------------------------------------|

| 1-2          | READY from GAL U11                          |

| 2-3          | READY directly from I/O expansion connector |

#### 2.7.8 Onboard UART Interrupt Select Jumper, JP9

The jumper JP9 is used to select which interrupt the onboard UART will use. Position 1-2 will cause an NMI interrupt. Position 2-3 will cause INT1.

#### Table 23: Onboard UART Interrupt Selection

| JP9 Position | Signal |

|--------------|--------|

| 1-2          | NMI    |

| 2-3          | INT1   |

This option is used to allow a debug monitor to be placed in ROM or for the serial port to be used with application software which requires interrupt masking.

#### 2.7.9 C50 Bootloader Enable Jumper, JP11

Jumper JP11 is used to enable or disable the on chip bootloader on the TMS320C5X. The table below describes the two positions:

#### Table 24: Bootload Enable/Disable

| JP11 Position | Function             |

|---------------|----------------------|

| 1-2           | Boot enabled on C50  |

| 2-3           | Boot disabled on C50 |

#### 2.7.10 Pseudo Boot Loader Enable Jumper, JP12

Jumper JP12 is used to indicate whether the pseudo boot loader is enabled on the EVM. This input is used by the memory decode logic. When the pseudo boot loader is enabled external flash is mapped in at 0x0000-0x7FFF in program space. When the pseudo loader is disabled the entire program space is RAM.

| JP12 Position | Device Selected             |

|---------------|-----------------------------|

| 1-2           | Pseudo Boot Loader Disabled |

| 2-3           | Pseudo Boot Loader Enabled  |

Table 25: Jumper JP12

#### 2.8 LEDs

The TMS320C230 EVM has two light emitting diodes. DS1 indicates the presence of +5 volts and is normally 'on' when power is applied to the EVM320C5X board. DS2 is under software control. It is tied to the XF signal on the DSP. These are shown in the table below:

#### Table 26: LEDs

| LED # | Color | Controlling Signal | On Signal State |

|-------|-------|--------------------|-----------------|

| DS1   | Green | +5 Volts           | 1               |

| DS2   | Red   | XF                 | 1               |

#### 2.9 Resets

There are multiple resets for the TMS320C50 EVM. The first reset is the power on reset. This circuit waits until power is within the specified range before releasing the power on reset pin to the TMS320C5X.

External sources such as the push button(SW1), Host reset pin 4 on P4 UART interface, and pin p13 on the Control connector P4 can generate a reset condition.

## Appendix A TMS320C5X EVM PAL Equations

This appendix lists the two PAL logic equations that are used on the TMS320C5X Evaluation Module (EVM).

| Topic |                         | Page |

|-------|-------------------------|------|

| A.1   | Memory Decode Equations | A-2  |

| A.2   | I/O Control Equations   | A-4  |

#### A.1 Memory Decode PAL Equations

The following PAL equations are used for the memory decode logic

/\*

- \*\* 503403.tdl

- \*\* Drawing Number: 503403

- \*\* Company: Spectrum Digital Inc

- \*\* Engineer: Ron Peterson

- \*\* 'G16V8' is defined (usually with the /D option).

\*/

| 503403 (in | is,      | /* io space */            |

|------------|----------|---------------------------|

| (          | ds,      | /* data space */          |

|            | ps,      | /* program space */       |

|            | rw,      | /* read write */          |

|            | stb,     | /* strobe */              |

|            | we,      | /* write strobe */        |

|            | rd,      | /* read strobe */         |

|            | br,      | /* Global Data Space */   |

|            | a15,     | /* address */             |

|            | out3,    | /* expanded rom enable */ |

|            | uart,    | /* UART CYCLE INPUT */    |

|            | opt0;    | /* Option 0 */            |

| out        | leprom,  | /* ROM cycle */           |

|            |          | /* RAM WRITE CYCLE */     |

|            | !ramoe,  | /* RAM READ CYCLE */      |

|            | !intern; | /* internal long cycle */ |

| )          | ,        | 5 7                       |

| {          |          |                           |

{

intern.oe = 1; ramoe.oe = 1; ramwe.oe = 1;eprom.oe = 1;

```

/* equations */

/* program space 0x8000-0xffff no out

ramoe = (!ps & rw & !stb & out3 & a15& opt0)

*/

( !ps & rw & !stb & !out3 & opt0 )

/* program space 0x0000-0xffff with out */

( !ps & rw & !stb & !opt0 )

/* program space 0x0000-0xffff psuedo disabled*/

/* data space 0x0000-0xffff no br

(!ds & rw & !stb & br)

*/

| (!ds & rw & !stb & !a15 & !br );

/* data space

0x0000-0x7fff with br

*/

*/

ramwe = (!ps & !rw & !stb)

/* program space 0x0000-0xffff

(!ds & !rw & !stb & br)

/* data space 0x0000-0xffff no br

*/

| (!ds & !rw & !stb & !a15 & !br );

/* data space 0x0000-0x7fff with br

*/

/* FLASH ROM (Bootload) external DATA SPACE 0x8000 - 0xffff ie br low */

*/

eprom = (a15 \& !br \& !we \& !ds \& out3)

/* Write Global Space 0x8000 with no out3

( a15 & !br & !rd & !ds & out3 )

/* Read Global space 0x8000 with no out3

*/

| (!a15 & !rd & !ps & out3 & opt0 ); /* Program space 0x0000-0x7fff no out3 psuedo en*/

/* 0xF000 in io space for UART chip */

intern = (a15 \& | br \& | we \& | ds \& out3)

/* Write to flash in global data space

*/

(!a15 & !rd & !ps & out3& opt0) /* Flash in program space 0x0000-0x7fff */

( a15 & !br & !rd & !ds & out3 )

/* Read from flash in global data space */

( !uart & !rd

)

/* UART Read */

| ( !uart & !we

/* UART Write */

);

putpart("g16v8", "503403A",

is, ps, ds, rw, stb, we, rd, br, out3, GND,

a15, eprom, _, ramwe, ramoe, opt0, _, uart, intern, VCC);

```

}

#### A.2 I/O Control PAL Equations

The following PAL equations are used for the I/O control logic

/\*

- \*\* 503404.tdl

- \*\* Drawing Number: 503404

- \*\* Company: Spectrum Digital Inc

- \*\* Engineer: Ron Peterson

\*\* 'G16V8' is defined (usually with the /D option).

\*/

| ,<br>503404 (in | clk,         | /* clock                 | */ |

|-----------------|--------------|--------------------------|----|

| ,               | is,          | /* io select             | */ |

|                 | rw,          | /* read write            | */ |

|                 | stb,         | /* strobe                | */ |

|                 | a15,         | /* address               | */ |

|                 | a14,         | /* address               | */ |

|                 | a13,         | /* address               | */ |

|                 | a12,         | /* address               | */ |

|                 | trdy,        | /* target ready          | */ |

|                 | !reset,      | /* reset                 | */ |

|                 | oe;          |                          |    |

| out             | ready;       | /* ready out             | */ |

|                 | io reg state | 0, /* io start machine 0 | */ |

|                 | state1,      | /* io state machine 1    | */ |

|                 | state2;      | /* io state machine 2    | */ |

| io              | uartwe,      | /* io write strobe       | */ |

|                 | uartrd,      | /* io read strobe        | */ |

|                 | uartcs;      | /* uart chip select      | */ |

| )               |              |                          |    |

{

group cntl\_state[state2,state1,state0];

|                                                                                        | /* SSS<br>/* TTT<br>/* 210<br>/*             | */<br>*/<br>*/                         |          |

|----------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------|----------|

| #define IDLE                                                                           | 0b111                                        | /* X                                   | */       |

| #define STATE1<br>#define STATE2<br>#define STATE3<br>#define STATE4<br>#define COMPLE | 0b011<br>0b001<br>0b000<br>0b010<br>TE 0b110 | /* 25<br>/* 50<br>/* 75<br>/* 75<br>/* | */<br>*/ |

| #define UNDEF0<br>#define UNDEF1                                                       |                                              | /*<br>/*                               | */<br>*/ |

TMS320C5X Evaluation Module Technical Reference

```

#define UART ( !is & !stb & a15 & a14 & a13 & a12 )

/* hook up output enables

*/

cntl_state.oe = !oe;

cntl_state.ck = clk;

/* hook up clocks

*/

/* state machines */

switch( cntl_state[] )

{

case IDLE:

if (reset)

cntl_state = IDLE;

else

{

if( UART )

cntl_state = STATE1;

else

cntl_state = IDLE;

}

break;

case STATE1:

if (reset)

cntl_state = IDLE;

else

{

cntl_state = STATE2;

}

break;

case STATE2:

if (reset)

cntl_state = IDLE;

else

{

cntl_state = STATE3;

}

break;

```

```

case STATE3:

if (reset)

cntl_state = IDLE;

else

{

cntl_state = STATE4;

}

break;

case STATE4:

if (reset)

{

cntl_state = IDLE;

}

else

{

cntl_state = COMPLETE;

}

break;

case COMPLETE:

if( reset )

{

cntl_state = IDLE;

}

else

{

if( UART )

cntl_state = COMPLETE;

else

cntl_state = IDLE;

}

break;

case UNDEF0:

cntl_state = IDLE;

break;

case UNDEF1:

cntl_state = IDLE;

break;

default:

cntl_state = IDLE;

break;

```

}

clk, is, rw, stb, a15, a14, a13, a12, trdy, GND, oe, uartwe, uartcs, state0, uartrd, state1, state2, reset, ready, VCC);

}

Spectrum Digital, Inc

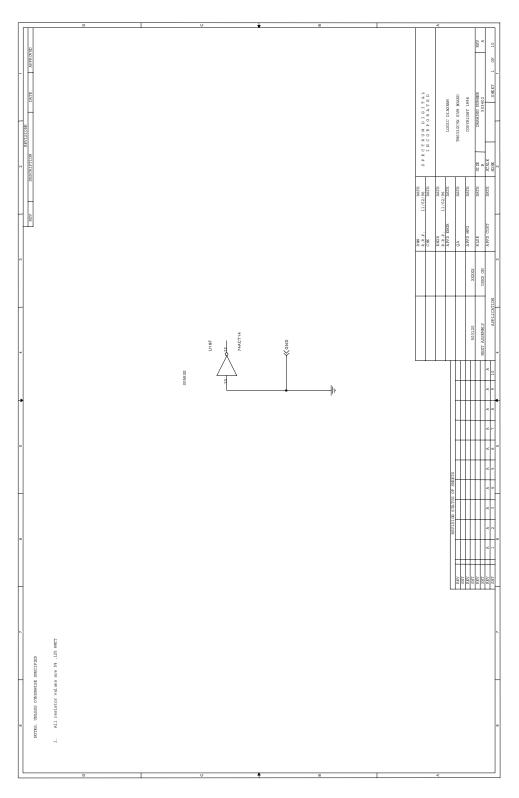

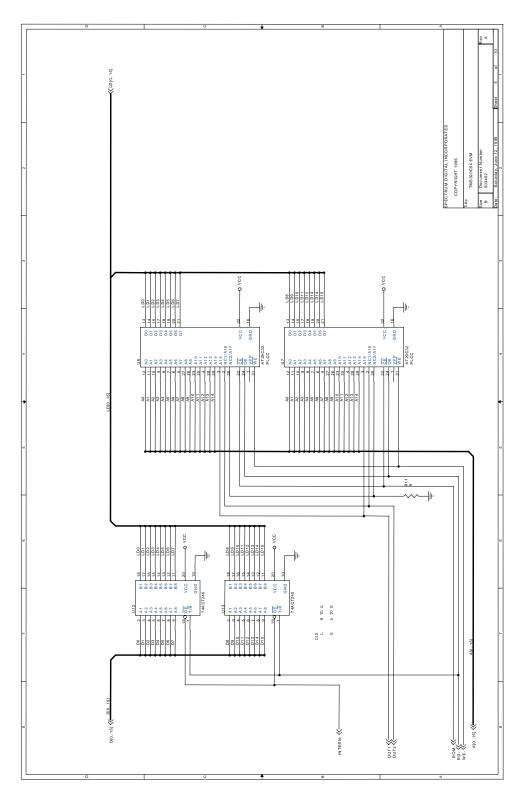

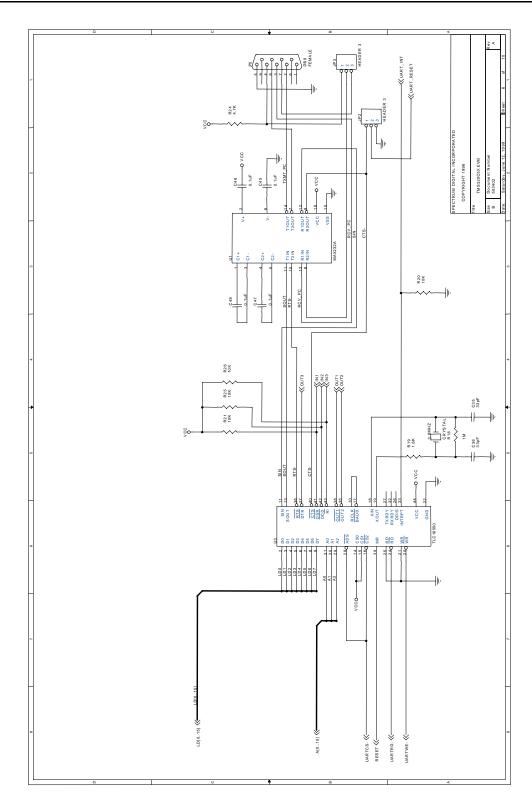

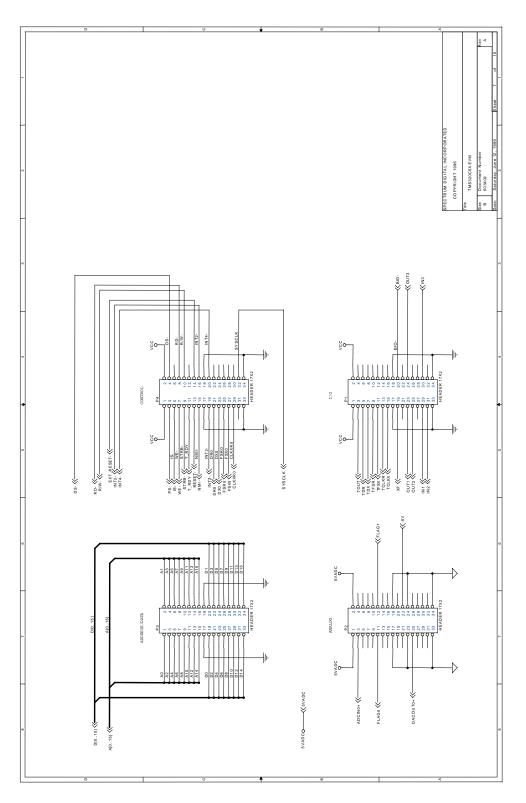

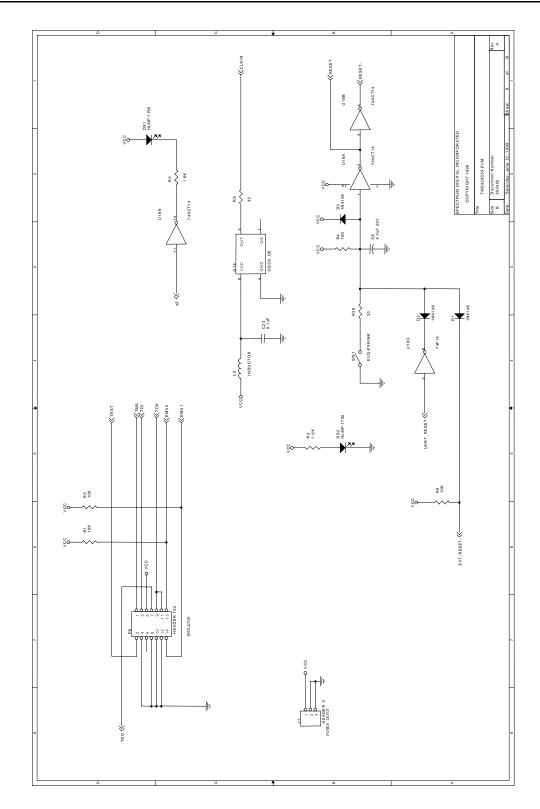

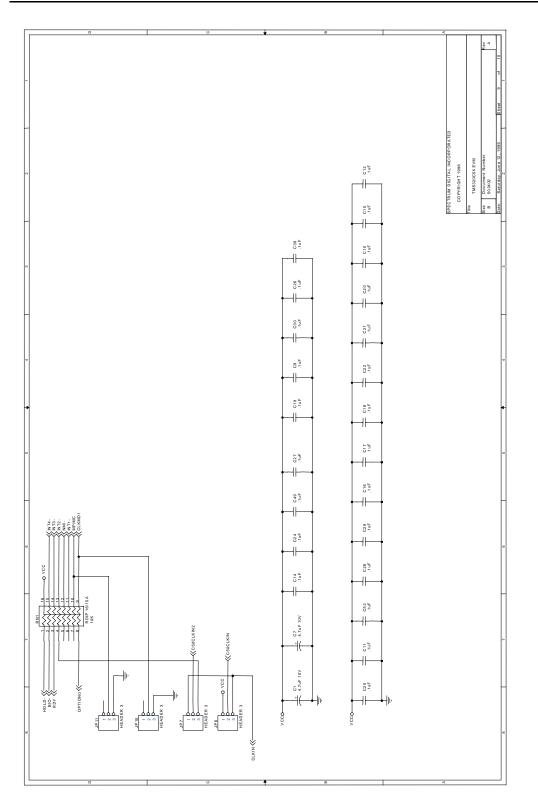

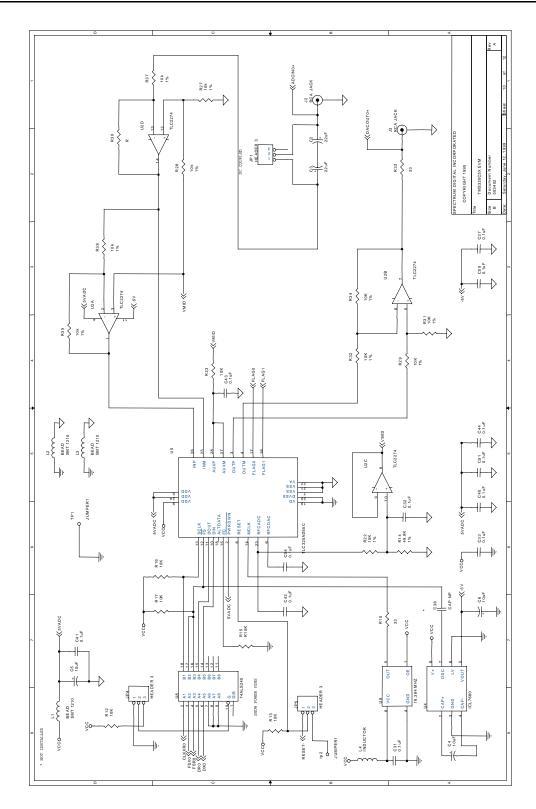

# Appendix B TMS320C5X EVM Schematics

This appendix contains the schematics for the TMS320C5X EVM. The schematics were drawn on ORCAD.

Spectrum Digital, Inc

TMS320C5X Evaluation Module Technical Reference

TMS320C5X Evaluation Module Technical Reference

Spectrum Digital, Inc

Spectrum Digital, Inc

# Appendix C TL16C550 Data Sheet

This appendix contains the programming data sheet for the TL16C550 Asynchronous Communications Element (ACE) used on the TMS320C5X Evaluation Module (EVM).

| Торіс  |                                   | Page |

|--------|-----------------------------------|------|

| C.1    | TL16C550 Serial Controller        | C-2  |

| C.1.1  | Detailed Description              | C-2  |

| C.1.2  | Line Control Register             | C-4  |

| C.1.3  | Line Status Register              | C-6  |

| C.1.4  | FIFO Control Register             | C-8  |

| C.1.5  | Modem Control Register            | C-9  |

| C.1.6  | Modem Status Register             | C-10 |

| C.1.7  | Divisor Latches                   | C-12 |

| C.1.8  | Scratchpad Register               | C-13 |

| C.1.9  | Interrupt Identification Register | C-13 |

| C.1.10 | Interrupt Enable Register         | C-15 |

| C.1.11 | Receiver                          | C-16 |

| C.1.12 | Master Reset                      | C-16 |

| C.1.13 | Programming                       | C-18 |

| C.1.14 | FIFO Polled Mode Operation        | C-19 |

## C.1 TL16C550 SERIAL CONTROLLER

The EVM320C5X uses a TL16C550 serial controller. The following sections describe the functionality of this device as it is used in the EVM320C5X.

The TL16C550 UART resides at address 0xF000 in the I/O address space on the EVM320C5X.

# C.1.1 DETAILED DESCRIPTION

Individual bits within the registers are referred to by the register mnemonic and the bit number in parenthesis. As an example, LCR (7) refers to line control register bit 7.

The transmitter buffer register and receiver buffer register are data registers that hold from five to eight bits of data. If less than eight data bits are transmitted, data is right justified to the LSB. Bit 0 of a data word is always the first serial data bit received and transmitted. The ACE data registers are double buffered so that read and write operations may be performed when the ACE is performing the parallel-to-serial or serial-to-parallel conversion.

The table below shows the I/O address of the various registers in the TL16C550 as they are used on the EVM320C5X. For more detailed use of this part refer to the appropriate data book.

| I/O<br>ADDRESS | REGISTER<br>MNEMONIC | REGISTER BIT NUMBERS                     |                                     |                                                              |                                   |                                                   |                                                             |                                                                                      |                                                                |

|----------------|----------------------|------------------------------------------|-------------------------------------|--------------------------------------------------------------|-----------------------------------|---------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------|

| RS232          |                      | BIT 7                                    | BIT 6                               | BIT 5                                                        | BIT 4                             | BIT 3                                             | BIT 2                                                       | BIT 1                                                                                | BIT 0                                                          |

| 0xF000         | RBR<br>(read only)   | Data                                     | Data                                | Data                                                         | Data                              | Data                                              | Data                                                        | Data                                                                                 | Data                                                           |

| 0xF000         | THR<br>(write only)  | Data                                     | Data                                | Data                                                         | Data                              | Data                                              | Data                                                        | Data                                                                                 | Data                                                           |

| 0xF000 t       | DLL                  | Bit7                                     | Bit6                                | Bit5                                                         | Bit4                              | Bit3                                              | Bit2                                                        | Bit1                                                                                 | Bit0                                                           |

| 0xF000 t       | DLM                  | Bit15                                    | Bit14                               | Bit13                                                        | Bit12                             | Bit11                                             | Bit10                                                       | Bit9                                                                                 | Bit8                                                           |

| 0xF001         | IER                  | 0                                        | 0                                   | 0                                                            | 0                                 | (EDSSI)<br>Enable<br>Modem<br>Status<br>Interrupt | (ELSI)<br>Enable<br>Receiver<br>line<br>status<br>interrupt | (ETBEI)<br>Enable<br>Transmit-<br>ter hold-<br>ing<br>register<br>empty<br>interrupt | (ERBI)<br>Enable<br>received<br>data<br>available<br>interrupt |

| 0xF002         | FCR<br>(write only)  | RCVR<br>Trigger<br>(MSB)                 | RCVR<br>Trigger<br>(LSB)            | Reserved                                                     | Reserved                          | DMA<br>mode<br>select                             | XMIT<br>FIFO<br>reset                                       | RCVR<br>FIFO<br>reset                                                                | FIFO<br>Enable                                                 |

| 0xF002         | IIR<br>(read only)   | FIFOs<br>Enabled tt                      | FIFOs<br>Enabled tt                 | 0                                                            | 0                                 | Int ID<br>Bit (2) tt                              | Int ID<br>Bit (1) tt                                        | Int ID<br>Bit (0)                                                                    | 0 if Int<br>Pending                                            |

| 0xF003         | LCR                  | (DLAB)<br>Divisor<br>latch<br>access bit | Set<br>break                        | Stick<br>parity                                              | (EPS)<br>Even<br>parity<br>select | (PEN)<br>Parity<br>Enable                         | (STB)<br>Num of<br>stop bits                                | (WLSB1)<br>Word len<br>select bit<br>1                                               | (WLSB0)<br>Word len<br>select bit<br>0                         |

| 0xF04          | MCR                  | 0                                        | 0                                   | 0                                                            | Loop                              | Enable<br>external<br>int (INT0<br>or INT1)       | OUT1<br>(an<br>unused<br>internal<br>signal)                | (RTS)<br>Request<br>to send                                                          | (DTR)<br>Data ter-<br>minal<br>ready                           |

| 0xF005         | LSR                  | Error in<br>RCVR<br>FIFOtt               | (TEMT)<br>transmit-<br>ter<br>empty | (THRE)<br>Transmit-<br>ter hold-<br>ing<br>register<br>empty | (BI)<br>Break<br>interrupt        | (FE)<br>Framing<br>Error                          | (PE)<br>Parity<br>Error                                     | (OE)<br>Overrun<br>error                                                             | (DR)<br>Data<br>ready                                          |

| 0xF006         | MSR                  | (DCD)<br>Data<br>carrier<br>detect       | (RI)<br>Ring<br>Indicator           | (DSR)<br>Data set<br>ready                                   | (CTS)<br>Clear to<br>send         | (DDCD)<br>Delta<br>data car-<br>rier detect       | (TERI)<br>Trailing<br>edge ring<br>indicator                | (DDSR)<br>Delta<br>data set<br>ready                                                 | (DCTS)<br>Delta<br>clear to<br>send                            |

| 0xF007         | SCR                  | Bit 7                                    | Bit 6                               | Bit 5                                                        | Bit 4                             | Bit 3                                             | Bit 2                                                       | Bit 1                                                                                | Bit 0                                                          |

## Table 1: SUMMARY OF ACCESSIBLE REGISTERS

t DLAB 1

tt These bits are always 0 when FIFOs are disabled.

## C.1.2 LINE CONTROL REGISTER (0xF003)

The format of the data character is controlled by the Line Control Register. The LCR may be read. Its contents are described below and shown in Figure 1.

LCR(0) and LCR(1) Word Length Select Bits:

| LCR1 | LCR0 | Data bits   |

|------|------|-------------|

| 0    | 0    | 5 data bits |

| 0    | 1    | 6 data bits |

| 1    | 0    | 7 data bits |

| 1    | 1    | 8 data bits |

LCR(2) Stop Bits Select Bit 2:

LCR(2) specifies the number of stop bits in each transmitted character as shown below and in table 21. The receiver always checks for one stop bit.

| LCR2 | Stop Bits                                  |  |  |

|------|--------------------------------------------|--|--|

| 0    | 1 Stop Bit                                 |  |  |

| 1    | 1.5 Stop bits if 5 data<br>bits selected   |  |  |

| 1    | 2 Stop bits if 6,7,8<br>data bits selected |  |  |

#### Table 3: STOP BIT SELECT

LCR(3) Parity Enable Bit 3:

When LCR(3) is high, a parity bit between the last data word bit and stop bit is generated and checked.

LCR(4) Even Parity Select Bit 4:

When enabled, a logic one selects even parity.

LCR(5) Stick Parity Bit 5:

When parity is enabled (LCR(3) = 1, LCR(5) = 1) causes the transmission and reception of a parity bit to be in the opposite state from the value of LCR(4). This forces parity to a known state and allows the receiver to check the parity bit in a known state.

LCR(6) Break Control Bit 6:

When LCR(6) is set to a logic 1, the serial output (SOUT1/SOUT0) is for forced to the spacing state (low). The break control bit acts only on the serial output and does not affect the transmitter logic. If the following sequence is used, no invalid characters will be transmitted because of the break:

- Step 1. Load a zero byte in response to the Transmitter Holding Register Empty (THRE) status indication.

- Step 2. Set the break in response to the next THRE status indication.

- Step 3. Wait for the transmitter to be idle when transmitter empty status signal is set high (TEMT=1). Then clear the break when the normal transmission has to be restored.

LCR(7) Divisor Latch Access Bit (DLAB) bit 7:

Bit 7 must be set high (logic 1) to access the divisor latches DLL and DLM of the baud rate generator during a read or write operation. LCR(7) must be input low (logic 0) to access the receiver buffer register, the transmitter holding register or the interrupt enable register.

## C.1.3 LINE STATUS REGISTER (0xF005)

The line status register (LSR) is a single register that provides status indications. The line status register shown in table 21 and described below:

## LSR(0) Data Ready (DR) Bit 0:

Data Ready is set high when an incoming character has been received and transferred into the receiver buffer register or the FIFO. LSR(O) is reset low by a CPU read of the data in the receiver buffer register or the FIFO.

## LSR(1) Overrun Error (OE) bit 1:

Overrun Error indicates that data in the receiver buffer register was not read by the CPU before the next character was transferred into the receiver buffer register overwriting the previous character. The OE indicator is reset whenever the CPU reads the contents of the line status register. An overrun error will occur in the FIFO mode after the FIFO is full and the next character is completely received. The overrun error is detected by the CPU on the first LSR read after it happens. The character in the shift register is not transferred to the FIFO but it is overwritten.

# LSR(2) Parity Error (PE) bit 2:

Parity Error indicates that the received data character does not have the correct parity as selected by LCR(3) and LCR(4). The PE bit is set high upon detection of a parity error and is reset low when the CPU reads the contents of the LSR. In the FIFO mode, the parity error is associated with a particular character in the FIFO, LSR(2) resets the error when the character is at the top of the FIFO.

#### LSR(3) Framing Error (FE) bit 3:

Framing error indicates that the received character did not have a valid stop bit. LSR(3) is set high when the stop bit following the last data bit or parity bit is detected as a zero bit (spacing level). The FE indicator is reset low when the CPU reads the contents of the LSR. In the FIFO mode, the framing error is associated with a particular character in the FIFO. LSR(3) reflects the error when the character is at the top of the FIFO.

LSR(4) Break Interrupt (BI) bit 4:

Break Interrupt is set high when the received data input is held in the spacing (logic 0) state for longer than a full word transmission time (start bit + data bits + parity + stop bits). The BI indicator is reset when the CPU reads the contents of the line status register. In the FIFO mode, this is associated with a particular character in the FIFO. LSR(2) reflects the BI when the break character is at the top of the FIFO. The error is detected by the CPU when its associated character is at the top of the FIFO during the first LSR read. Only one zero character is loaded into the FIFO when BI occurs.

LSR(4) - LSR(1) are the error conditions that produce a receiver line status interrupt (priority 1 interrupt in the Interrupt Identification register(IIR)) when any of the conditions are detected. This interrupt is enabled by setting IER(2) = 1 in the interrupt enable register.

LSR(5) Transmitter Holding Register Empty (THRE) bit 5:

THRE Indicates that the ACE is ready to accept a new character for transmission. The THRE bit is set high when a character is transferred from the transmitter holding register into the transmitter shift register. LSR(5) is reset low by the loading of the transmitter holding register by the CPU. LSR(5) is not reset by a CPU read of the LSR. In the FIFO mode when the XMIT FIFO is empty, this bit is set. It is cleared when one byte is written to the XMIT FIFO. When the THRE Interrupt is enabled by IER(1), THRE causes a priority 3 interrupt in the IIR. If THRE is the interrupt source indicated In IIR, INTRPT is cleared by a read of the IIR.

LSR(6) Transmitter Empty (TEMT) bit 6:

TEMT is set high when the Transmitter Holding Register(THR) and the Transmitter Shift Register(TSR) are both empty. LSR(6) is reset low when a character is loaded into the THR and remains low until the character is transferred out of SOUT. TEMT is not reset low by a CPU read of the LSR. In FIFO mode, when both the transmitter FIFO and shift register are empty, this bit is set to one.

LSR(7) RCVR FIFO error bit 7:

The LSR(7) bit is always 0 in the TL16C450 mode. In FIFO mode, it is set when at least one of the following data errors is in the FIFO: parity error, framing error, or break interrupt indication. It is cleared when the CPU reads the LSR if there are no subsequent errors in the FIFO.

# NOTE:

The line status register may be written. However, this function is intended only for factory test. It should be considered as read only by applications software.

## C.1.4 FIFO CONTROL REGISTER (0xF002)

This write only register is at the same location as the IIR. It is used to enable and clear the FIFOs, set the trigger level of the RCVR FIFO, and select the type of DMA signaling.

## FCR(0) FIFO Enable

FIFO enables both the XMIT and RCVR FIFOS. All bytes in both FIFOs can be cleared by resetting FCR(0). Data is cleared automatically from the FIFOs when changing from the FIFO mode to the TL16C450 mode and vice versa. Programming of other FCR bits is enabled by setting FCR(0) = 1.

#### FCR(1) Receiver FIFO Reset

FCR(1) = 1 clears all bytes In the RCVR FIFO and resets the counter logic to 0. This does not clear the shift register.

#### FCR(2) Transmit FIFO Reset

FCR(2) = 1 clears all bytes In the XMIT FIFO and resets the counter logic to 0. This does not clear the shift register.

## FCR(3) DMA Mode Select

FCR(3) = 1 will change the RXRDY and TXRDY pins from mode 0 to mode 1 if FCR(0) = 1.

## FCR(4) - FCR(5):

These two bits are reserved for future use.

#### FCR(6-7) FIFO Receiver Trigger

These two bits are used for setting the trigger level for the RCVR FIFO Interrupt a follows:

| Bit 7 | Bit 6 | Receiver Fifo<br>Trigger Level (Bytes) |

|-------|-------|----------------------------------------|

| 0     | 0     | 1                                      |

| 0     | 1     | 4                                      |

| 1     | 0     | 8                                      |

| 1     | 1     | 14                                     |

Table 4: FIFO Trigger Levels

## C.1.5 MODEM CONTROL REGISTER (0xF004)

The Modem Control Register (MCR) controls the interface with the modem or data set as described in Figure 2. MCR can be written and read. The RTS and DTR outputs are directly controlled by their control bits in this register. A high input asserts a low(true) at the output pins. MCR bits 0, 1, 2, 3, and 4 are shown as follows:

```

MCR(0) Data Terminal Ready

```

When MCR(0) is set high, the DTR output is forced low. When MCR(0) is reset low, the DTR output is forced high. The DTR output of the serial channel may be input into an inverting line driver in order to obtain the proper polarity input at the modem or data set.

#### MCR(1) Request to Send

When MCR(1) is set high, the RTS output is forced low. When MCR(1) is reset low, the RTS output is forced high. The RTS output of the serial channel may be input into an inverting line driver to obtain the proper polarity input at the modem or data set.

# MCR(2) OUT1

When MCR(2) is set high, OUT1 is forced low.

MCR(3) OUT2

When MCR(3) is set high, the OUT2 output is forced low.

#### MCR(4) Loop

MCR(4) provides a local loopback feature for diagnostic testing of the channel. When MCR(4) is set high, serial output (SOUT) is set to the marking (logic 1) state, and the receiver data input serial input (SIN) is disconnected. The output of the transmitter shift register is looped back into the receiver shift register input. The four modem control inputs (CTS, DSR, DCD, and RI) are disconnected. The modem control outputs (DTR, RTS, OUT1, and OUT2) are internally connected to the four modem control inputs. The modem control outputs pins are forced to their inactive state(high) on the TL16C550. In the diagnostic mode, data transmitted is immediately received. This allows the processor to verify the transmission and receive data paths of the selected serial channel. Interrupt control is fully operational. However, interrupts are generated by controlling the lower four MCR bits internally. Interrupts are not generated by activity on the external pins represented by those four bits.

MCR(5) - MCR(7) are permanently set to logic 0.

# C.1.6 MODEM STATUS REGISTER (0xF006)

The MSR provides the CPU with status of the modem input lines from the modem or peripheral devices The MSR allows the CPU to read the serial channel modem signal inputs by accessing the data bus interface of the ACE in addition to the current status of four bits of the MSR that indicate whether the modem in inputs changed since the last reading of the MSR. The delta status bits are set high when a control input from the modem changes state and reset low when the CPU reads the MSR.

The modem input lines CTS, DSR, RI and DCD. MSR(4) - MSR(7) are status indications of these lines. A status bit = 1 indicates the input is a low. A status bit = 0 indicates the input is high. If the modem status interrupt in the interrupt enable register is enabled IER(3), an interrupt is generated whenever MSR(0) - MSR(3) is set to a one. The MSR is a priority 4 interrupt. The contents of the Modem Status Register are described in Table 3.

MSR(0) Delta Clear to Send (DCTS) bit 0:

DCTS displays that the CTS input to the serial channel has changed state since it was last read by the CPU.

MSR(1) Delta Data Set Ready (DDSR) bit 1:

DDSR indicates that the DSR input to the serial channel has changed state since the last time it was read by the CPU.

MSR(2) Trailing Edge of Ring Indicator (TERI) bit 2: